## UNIVERSIDAD DE CÓRDOBA

# Departamento de Arquitectura de Computadores, Electrónica y Tecnología Electrónica

## **TESIS DOCTORAL**

## Programming issues for video analysis on Graphics Processing Units

Juan Gómez Luna

Córdoba, Febrero de 2012

A mis padres, por enseñarme el camino A Virginia y a Nicolás, por recorrerlo conmigo

# Agradecimientos

Con la satisfacción de haber llegado al final y después del esfuerzo realizado, hay que mirar atrás para agradecer su apoyo a todos los que han hecho posible la consecución de esta meta.

En primer lugar, a mis directores Dr. José María González Linares, Dr. José Ignacio Benavides y Dr. Nicolás Guil, por haberme orientado tan certeramente. Me siento afortunado por trabajar en condiciones de exigencia y rigor.

A mis compañeros del Departamento de Arquitectura de Computadores, Electrónica y Tecnología Electrónica de la Universidad de Córdoba, en especial a Edmundo Sáez por su ayuda en los inicios. También a los compañeros del Departamento de Arquitectura de Computadores de la Universidad de Málaga, particularmente a Juan Lucena, por su habilidad resolviendo problemas hardware, y a Fran, por sus orientaciones en la preparación de este documento.

Al Vicerrectorado de Política Científica y al Vicerrectorado de Estudios de Posgrado y Formación Continua de la Universidad de Córdoba, por toda la ayuda prestada.

Al profesor Walter Stechele, de la Universidad Técnica de Munich, por darme la posibilidad de hacer la estancia allí y por facilitarme todos los trámites para la consecución del Doctorado Europeo. Por supuesto, a Holger Endt, de BMW Forschung und Technik. También, a los profesores Hans-Joachim Bungartz y Noel O'Connor por elaborar los informes sobre mi tesis.

A Nacho, Marisa y Miguel Ángel, por acogerme tan bien en Málaga.

A mi padre, Pedro, por ser mi mentor en la tesis y en todo lo demás; a mi madre, Mercedes, por escucharme siempre y por hacer todo por ayudarme; y a mis hermanos, Fernando y Pedro, porque me gusta que seamos tres diferentes implementaciones de la misma arquitectura. Y, por supuesto, a Loli, por lo bien que me prepara el *hatillo* cada vez que paso por casa.

Por último, a Virginia por ser la motivación y la recompensa, por compartir lo bueno y lo malo incondicionalmente ("Bajo el título estará mi nombre, que traducido significará el tuyo"). Y a mi pequeño Nicolás por darle sentido a todo.

# **Contents**

| Lis | t of 1  | Figures                                                         | vi |

|-----|---------|-----------------------------------------------------------------|----|

| Lis | st of T | Tables                                                          | ix |

| 1   | Vid     | leo analysis on Graphics Processing Units                       | 1  |

|     | 1.1     | Introduction                                                    | 1  |

|     |         | 1.1.1 Parallelism as the key for improving computer performance | 2  |

|     |         | 1.1.2 Recent evolution of parallel hardware                     | 2  |

|     |         | 1.1.3 Parallel programming models                               | 4  |

|     | 1.2     | Programming GPUs for general-purpose processing                 | 5  |

|     |         | 1.2.1 A few words on CUDA                                       | 6  |

|     |         | 1.2.2 Conditions and bottlenecks for GPU performance            | 6  |

|     |         | 1.2.3 Generic optimization techniques on GPUs                   | 7  |

|     | 1.3     | Towards video processing optimization on GPU                    | 10 |

|     |         | 1.3.1 State of the art of video and image processing on GPU     | 11 |

|     |         | 1.3.2 Efficient mapping of video analysis applications on GPU   | 12 |

|     |         | 1.3.3 Stream processing paradigm for video analysis on GPU      | 13 |

|     |         | 1.3.4 Aims of this work                                         | 16 |

|     | 1.4     | Structure of this document                                      | 16 |

| 2   | An      | introduction to GPU computing with CUDA                         | 19 |

|     | 2.1     | Graphics processing units as general-purpose processors         | 19 |

|     | 2.2     | CUDA-enabled devices                                            | 21 |

|     | 2.3     | CUDA programming model                                          | 21 |

|     |         | 2.3.1 Thread hierarchy                                          | 21 |

|     |         | 2.3.2 Memory hierarchy                                          | 23 |

|     | 2.4     | Hardware implementation                                         | 23 |

|      | 2.4.1     | SIMT architecture and multithreading                                         | 24 |

|------|-----------|------------------------------------------------------------------------------|----|

|      | 2.4.2     | Streaming multiprocessors                                                    | 24 |

|      | 2.4.3     | Memory spaces                                                                | 26 |

| 3 Ta | rget app  | lications                                                                    | 31 |

| 3.1  | Introdu   | action                                                                       | 31 |

| 3.2  | Histog    | ram calculation                                                              | 32 |

|      | 3.2.1     | Discussion                                                                   | 32 |

| 3.3  | Egomo     | otion compensation and moving objects detection algorithm                    | 33 |

|      | 3.3.1     | Discussion                                                                   | 38 |

| 3.4  | The Go    | eneralized Hough Transform                                                   | 39 |

|      | 3.4.1     | Discussion                                                                   | 42 |

| 3.5  | Conclu    | asions                                                                       | 44 |

| 4 Hi | ghly opti | imized histogram calculation on GPU                                          | 47 |

| 4.1  | Introdu   | action                                                                       | 47 |

| 4.2  | Related   | d work                                                                       | 49 |

| 4.3  | A micr    | robenchmark-based study of the shared memory                                 | 50 |

|      | 4.3.1     | Methodology and initial observations                                         | 51 |

|      | 4.3.2     | Warp access patterns                                                         | 52 |

|      | 4.3.3     | Non-atomic access                                                            | 53 |

|      | 4.3.4     | Atomic access                                                                | 54 |

| 4.4  | An opt    | cimized approach to histogram generation in shared memory                    | 65 |

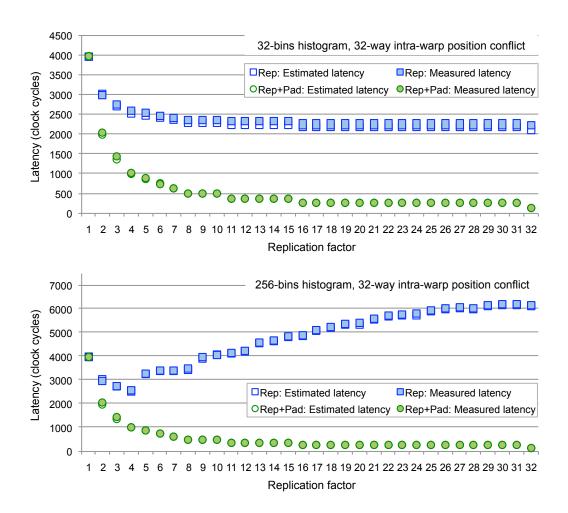

|      | 4.4.1     | Replication                                                                  | 66 |

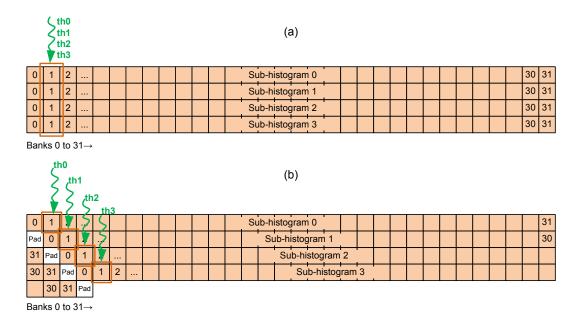

|      | 4.4.2     | Padding                                                                      | 68 |

|      | 4.4.3     | Interleaved read access                                                      | 68 |

| 4.5  | Experi    | mental evaluation                                                            | 69 |

|      | 4.5.1     | Evaluation of the optimization techniques                                    | 70 |

|      | 4.5.2     | Thorough evaluation of our approach and comparison to related works          | 73 |

|      | 4.5.3     | Histogram-based kernels for color images                                     | 74 |

|      | 4.5.4     | Discussion                                                                   | 75 |

|      | 4.5.5     | Evaluation of the $\mathcal{R}$ -per-block approach on older GPU generations | 76 |

| 4.6  | Experi    | ences with replication in global memory                                      | 77 |

| 4.7  | Conclu    | asions                                                                       | 77 |

| 5 | Effi | cient wo | rk distribution                                                       | 81  |

|---|------|----------|-----------------------------------------------------------------------|-----|

|   | 5.1  | Introduc | ction                                                                 | 81  |

|   | 5.2  | Dealing  | with sequential parts                                                 | 82  |

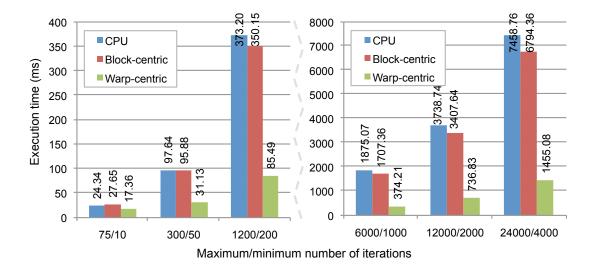

|   |      | 5.2.1    | SISD and SIMD computing on the GPU                                    | 83  |

|   |      | 5.2.2    | Experimental evaluation                                               | 84  |

|   | 5.3  | Re-orga  | nizing the workload                                                   | 85  |

|   |      | 5.3.1    | Reducing memory accesses and executed instructions through compaction | 86  |

|   |      | 5.3.2    | Minimizing warp divergence through sorting                            | 87  |

|   |      | 5.3.3    | Experimental evaluation                                               | 87  |

|   | 5.4  | Load ba  | llancing versus occupancy maximization                                | 89  |

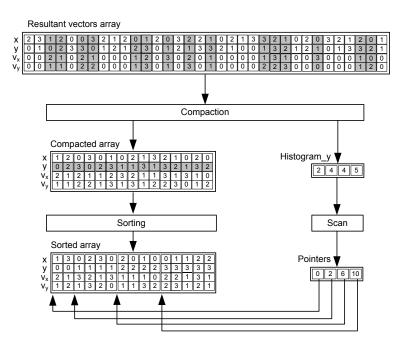

|   |      | 5.4.1    | Applying compaction and sorting to the GHT                            | 89  |

|   |      | 5.4.2    | Work distribution among blocks and threads                            | 92  |

|   |      | 5.4.3    | Application of the mechanisms                                         | 94  |

|   |      | 5.4.4    | Experimental evaluation                                               | 96  |

|   | 5.5  | Conclus  | sions                                                                 | 100 |

| 6 | Stre | eam proc | cessing on GPU with CUDA streams                                      | 101 |

|   | 6.1  | Introduc | ction                                                                 | 101 |

|   | 6.2  | CUDA     | streams                                                               | 103 |

|   | 6.3  | Charact  | erizing the behavior of CUDA streams                                  | 105 |

|   |      | 6.3.1    | A thorough observation of CUDA streams                                | 106 |

|   |      | 6.3.2    | CUDA streams performance models                                       | 110 |

|   | 6.4  | Testing  | the streams with SDK-based applications                               | 112 |

|   |      | 6.4.1    | Matrix multiplication                                                 | 113 |

|   |      | 6.4.2    | 256-bins histogram                                                    | 115 |

|   |      | 6.4.3    | RGB to grayscale conversion                                           | 117 |

|   | 6.5  | Optimiz  | zed stream processing with CUDA streams                               | 118 |

|   |      | 6.5.1    | Adaptation to variable kernel computation time                        | 118 |

|   | 6.6  | Conclus  | sions                                                                 | 120 |

| 7 | Con  | clusions |                                                                       | 123 |

|   | 7.1  | Conclus  | sions and main contributions                                          | 123 |

|   | 7.2  | Publicat | tions related to this dissertation                                    | 125 |

|   |      | 7.2.1    | Publications in conference proceedings                                | 126 |

|   |      | 7.2.2    | Publications in journals                                              | 126 |

|   |      |          |                                                                       |     |

|              | 7.2.3   | Technical reports                                     | 127 |

|--------------|---------|-------------------------------------------------------|-----|

|              | 7.2.4   | Articles under review                                 | 127 |

| 7.3          | Future  | research                                              | 128 |

| A Res        | sumen d | le la tesis doctoral en castellano                    | 131 |

| <b>A.</b> 1  | Paralel | ización eficiente de las aplicaciones de vídeo en GPU | 131 |

| A.2          | Stream  | processing para análisis de vídeo en GPU              | 133 |

| A.3          | Princip | pales aportaciones                                    | 133 |

| A.4          | Conclu  | siones y trabajos futuros                             | 134 |

| Bibliography |         |                                                       |     |

# **List of Figures**

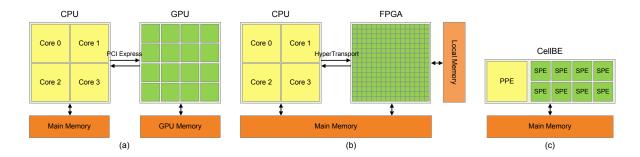

| 1.1  | Schematic of heterogeneous architectures                         | 3  |

|------|------------------------------------------------------------------|----|

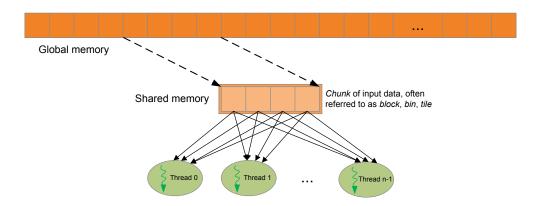

| 1.2  | Blocking/tiling in shared memory                                 | 8  |

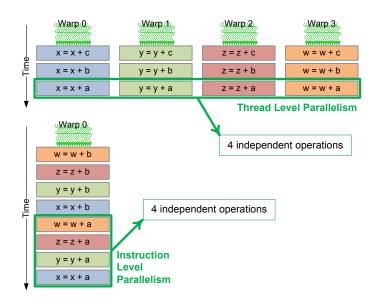

| 1.3  | Thread Level Parallelism vs. Instruction Level Parallelism       | 8  |

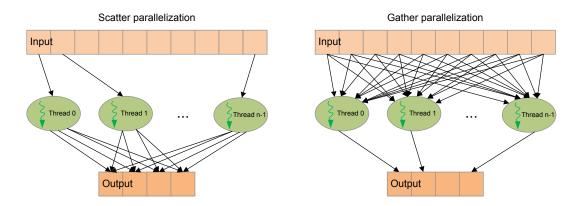

| 1.4  | Scatter and gather parallelization                               | 9  |

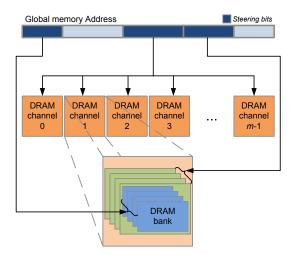

| 1.5  | Global memory organization and addresses                         | 10 |

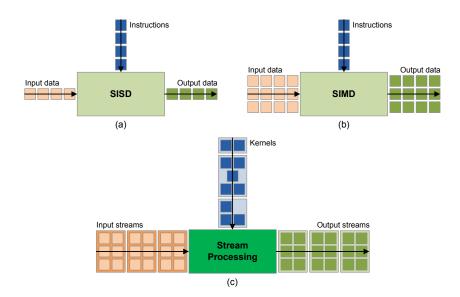

| 1.6  | SISD, SIMD and stream processing                                 | 14 |

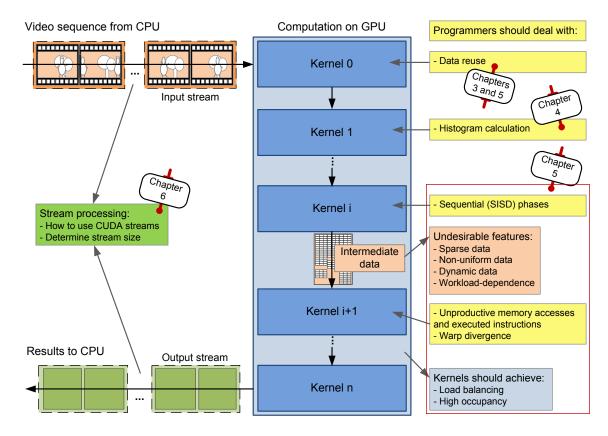

| 1.7  | Programming issues tackled in this dissertation                  | 17 |

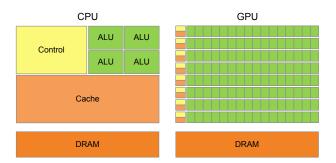

| 2.1  | Comparison of CPU and GPU architectures                          | 20 |

| 2.2  | CUDA programming model                                           | 23 |

| 2.3  | Streaming multiprocessor in c.c. 1.x                             | 25 |

| 2.4  | Streaming multiprocessor in c.c. 2.0                             | 26 |

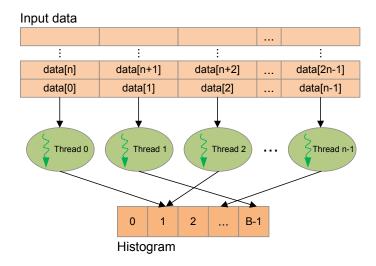

| 3.1  | Parallel histogram calculation                                   | 33 |

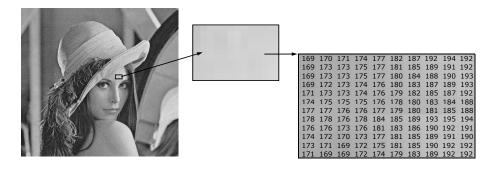

| 3.2  | Spatial locality in a grayscale image                            | 33 |

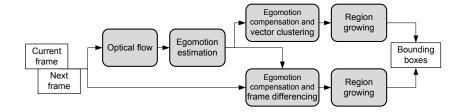

| 3.3  | Scheme of an optical flow based motion detection algorithm       | 34 |

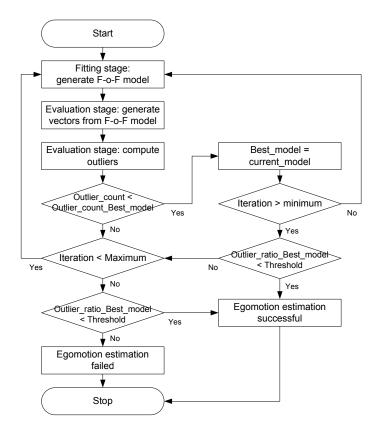

| 3.4  | Flow diagram for egomotion estimation with RANSAC                | 35 |

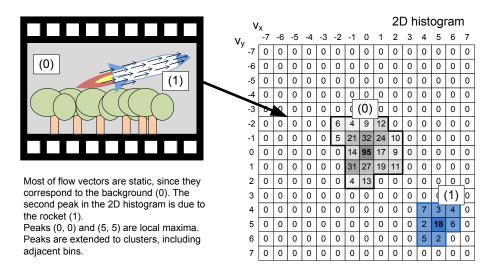

| 3.5  | 2D histogram used for vector clustering                          | 36 |

| 3.6  | Captures of two videos                                           | 37 |

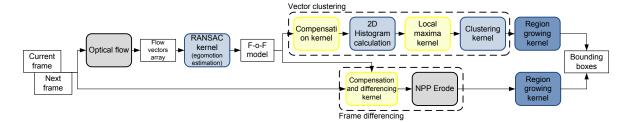

| 3.7  | GPU implementation of a moving objects detection algorithm       | 38 |

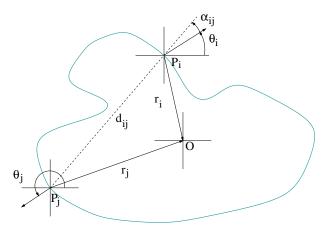

| 3.8  | Variables defined in the GHT                                     | 40 |

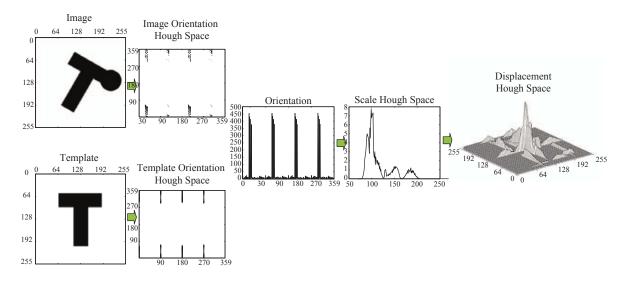

| 3.9  | Template, image and Hough spaces generated by the Fast GHT       | 41 |

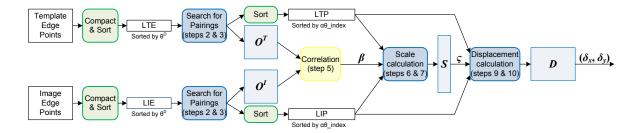

| 3.10 | GPU implementation of the Fast GHT                               | 42 |

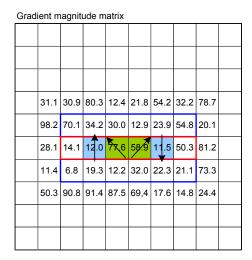

| 3.11 | Non-maximum suppression in Canny edge detection                  | 43 |

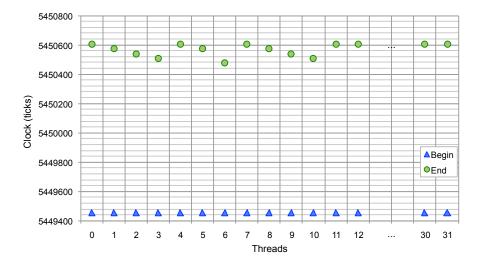

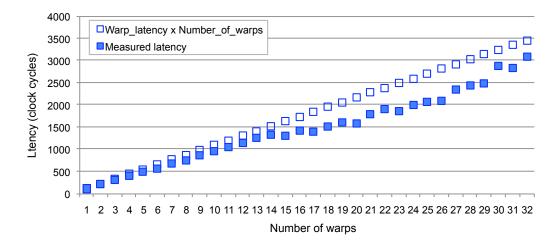

| 4.1  | Timeline for a warp access pattern to shared memory              | 52 |

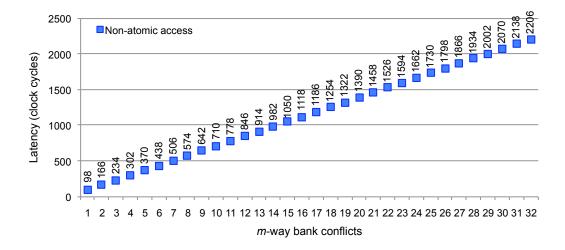

| 4.2  | Latency in clock cycles of non-atomic access to shared memory    | 54 |

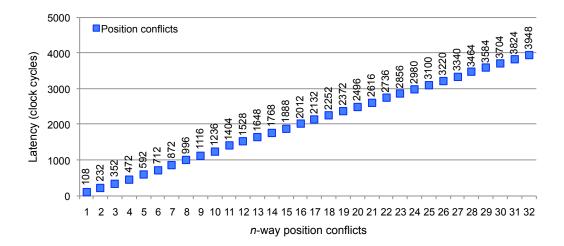

| 4.3  | Latency in clock cycles of atomic access with position conflicts | 55 |

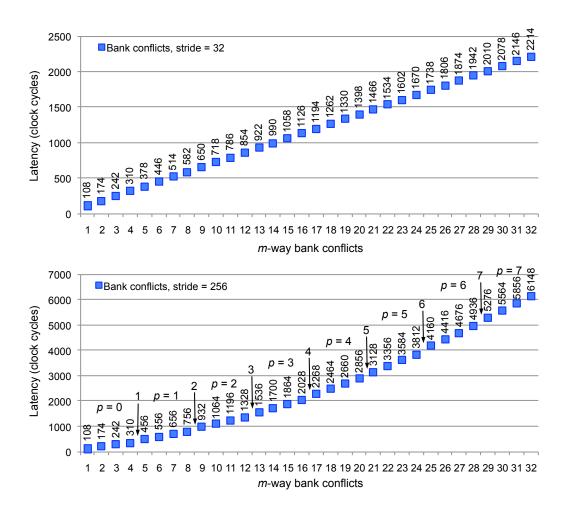

| 44   | Latency in clock cycles of atomic access with bank conflicts     | 56 |

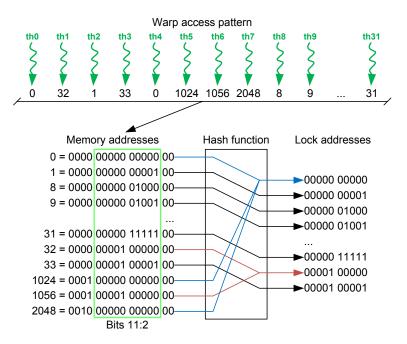

| 4.5  | Implementation of hash function in lock mechanism                               | 59  |

|------|---------------------------------------------------------------------------------|-----|

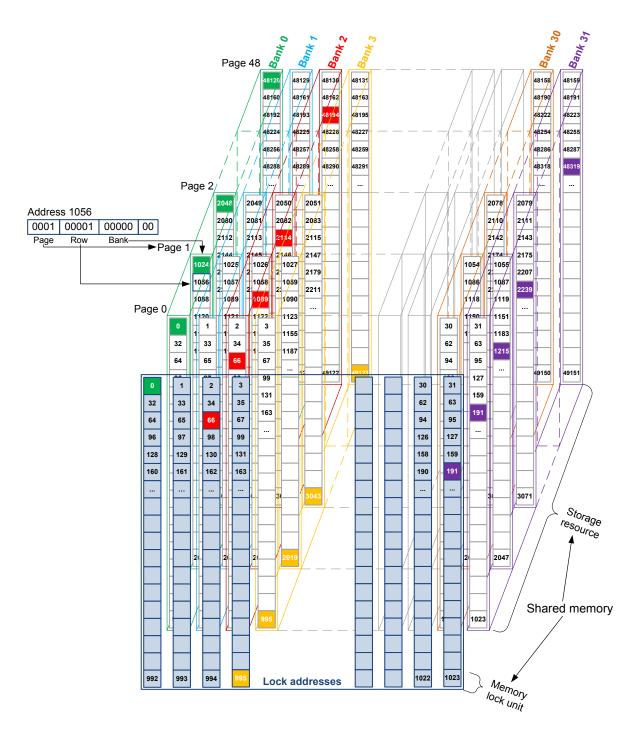

| 4.6  | Schematic of the shared memory                                                  | 60  |

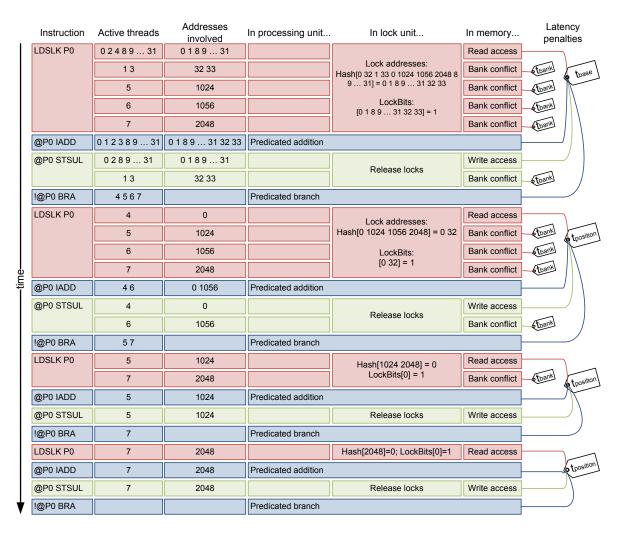

| 4.7  | Timeline for execution of instructions performing an atomic addition            | 61  |

| 4.8  | Execution time in milliseconds (ms) for 16 warps accessing 32 to 512 positions  | 64  |

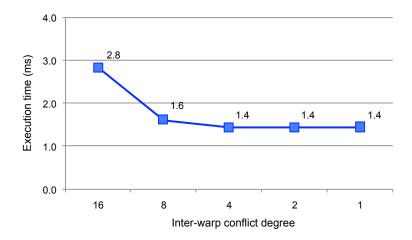

| 4.9  | Latency in clock cycles due to inter-warp conflicts                             | 65  |

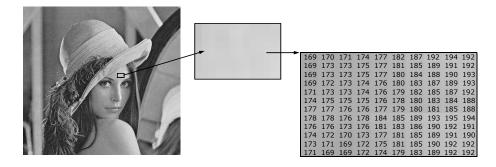

| 4.10 | Detail of a Lenna's grayscale image                                             | 66  |

| 4.11 | Replication in shared or global memory                                          | 67  |

| 4.12 | Degenerate case in a 32-bin histogram in shared memory                          | 69  |

| 4.13 | Latency in clock cycles for a 32-way position conflict                          | 70  |

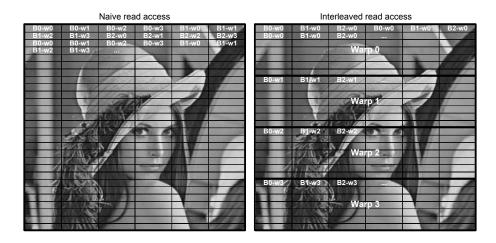

| 4.14 | Naive and interleaved read accesses                                             | 71  |

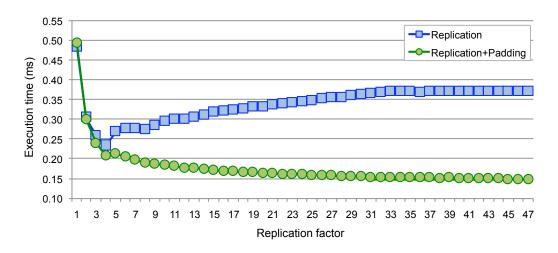

| 4.15 | Execution time for 256-bin histogram calculation with replication and padding   | 71  |

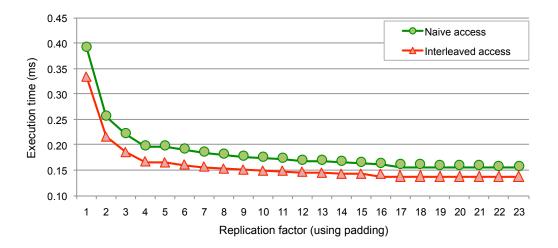

| 4.16 | Execution time for 256-bin histogram calculation with interleaved read access   | 73  |

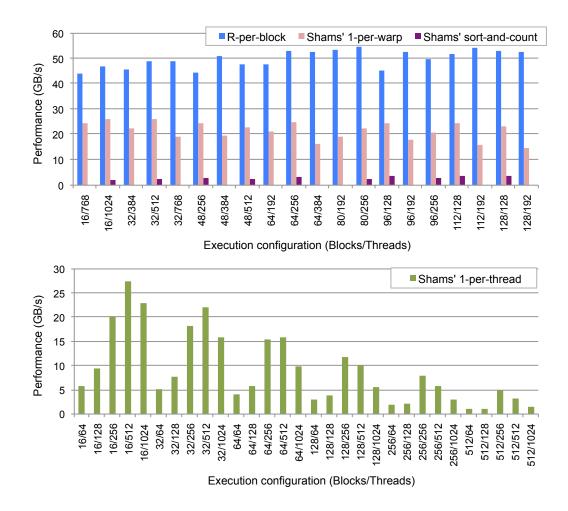

| 4.17 | Performance in gigabytes per second of 256-bins histogram calculation           | 74  |

| 4.18 | Average execution time in milliseconds of the displacement calculation          | 78  |

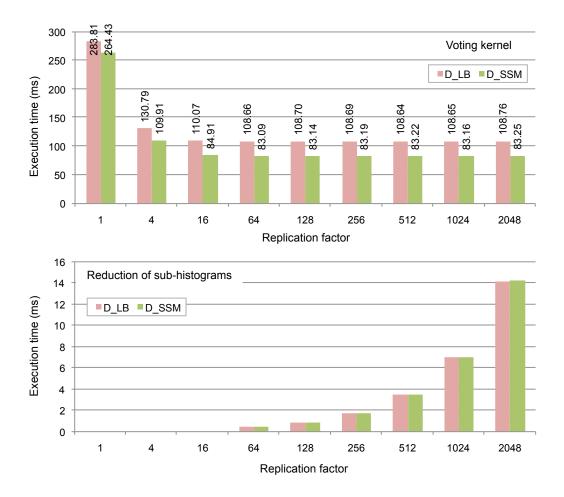

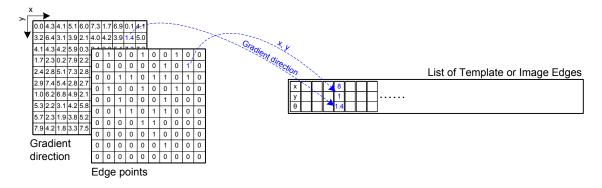

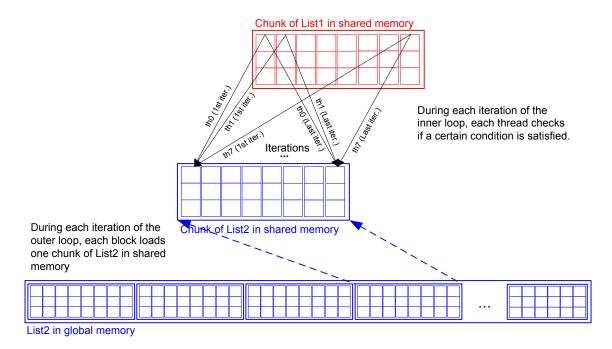

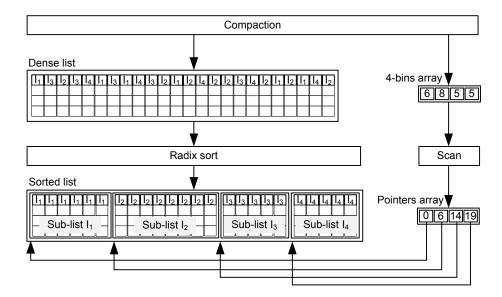

| 5.1  | Execution results of block-centric and warp-centric RANSAC implementations      | 85  |

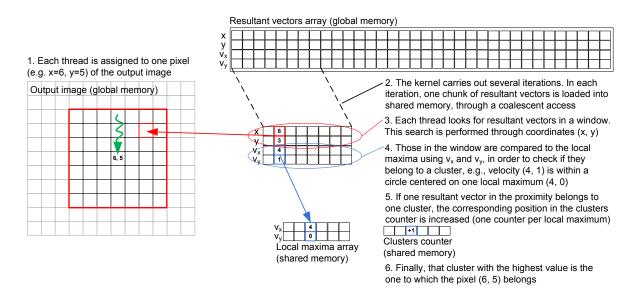

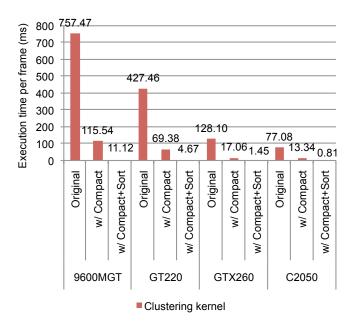

| 5.2  | GPU implementation of clustering kernel                                         | 86  |

| 5.3  | Compaction and sorting applied to the resultant vectors array                   | 88  |

| 5.4  | Performance impact of compaction and sorting on clustering kernel               | 88  |

| 5.5  | Compaction: contour points are compacted into a List of Edges                   | 90  |

| 5.6  | BASE strategy                                                                   | 90  |

| 5.7  | Dense list sorting using index $I$ as a key $\ldots$                            | 91  |

| 5.8  | Load-balancing mechanism                                                        | 93  |

| 5.9  | Save-shared-memory mechanism                                                    | 94  |

| 5.10 | Comparison between SSM and LB using a synthetic sorted list                     | 99  |

| 6.1  | Comparison of timelines for sequential and concurrent copy and kernel execution | 104 |

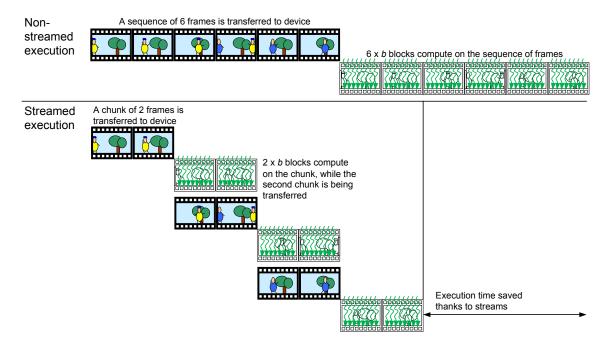

| 6.2  | Computation on a sequence of 6 frames for non-streamed and streamed execution   | 105 |

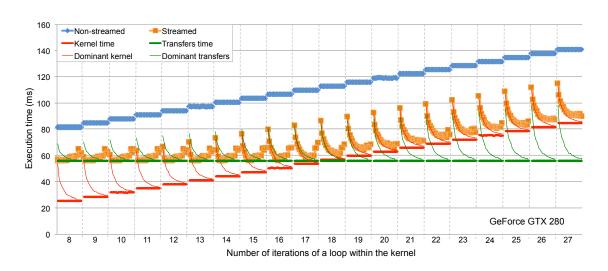

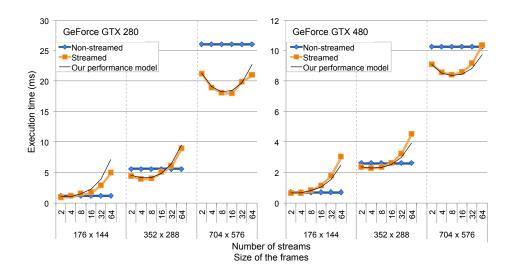

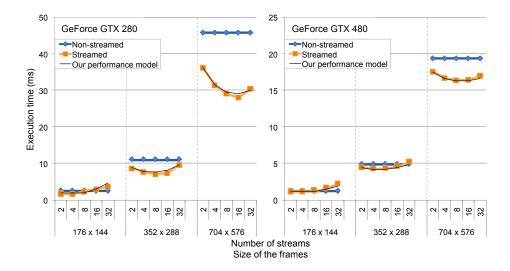

| 6.3  | First observations of CUDA streams on GeForce GTX 280                           | 107 |

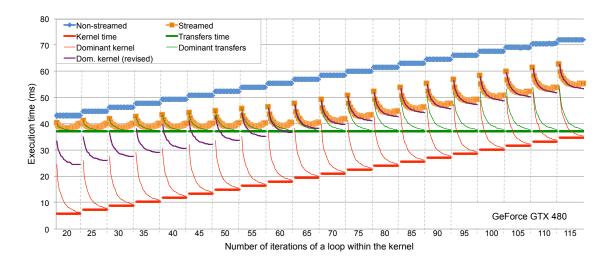

| 6.4  | First observations of CUDA streams on GeForce GTX 480                           | 108 |

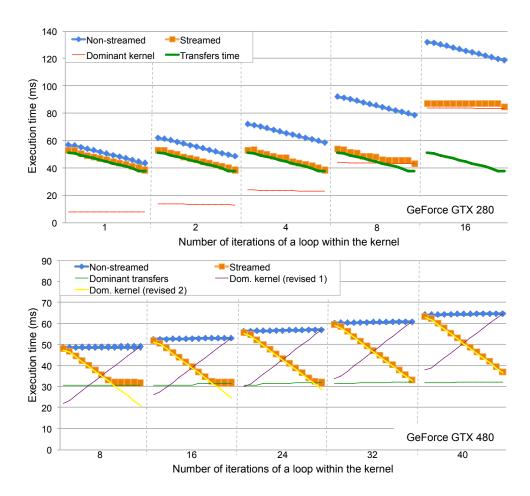

| 6.5  | Second observations of CUDA streams on GeForce GTX 280 and GTX 480              | 110 |

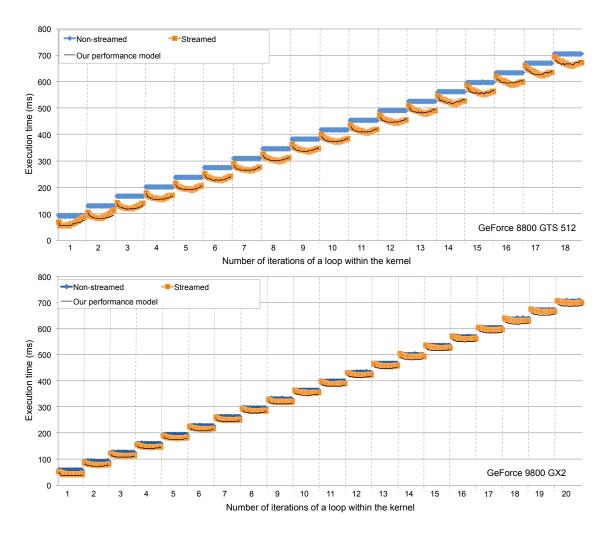

| 6.6  | Validation of performance model on devices with compute capability 1.1          | 113 |

| 6.7  | Validation of performance model on devices with compute capability 1.2/1.3      | 114 |

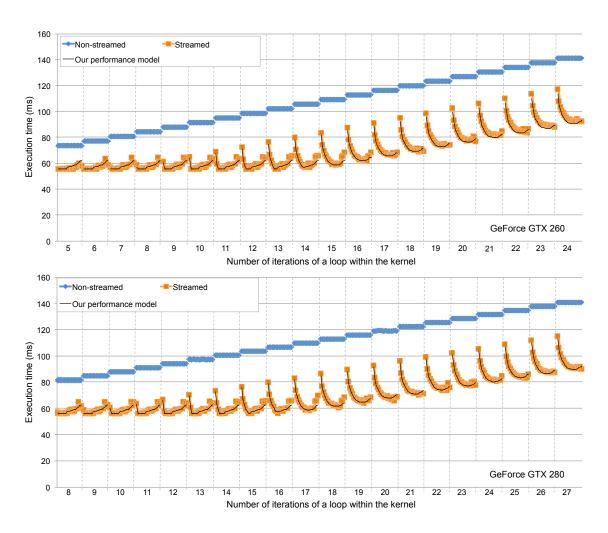

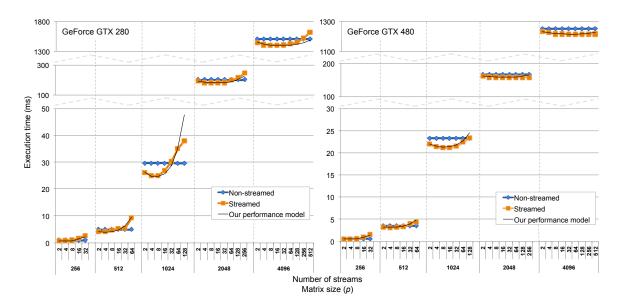

| 6.8  | Validation of performance model on devices with compute capability 2.0          | 115 |

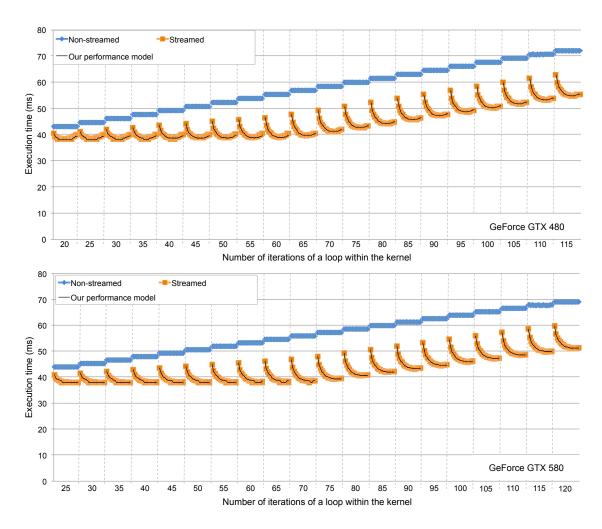

| 6.9  | Execution time for streamed matrix multiplication                               | 116 |

| 6.10 | Execution time for streamed 256-bins histogram computation of 64 frames         | 116 |

| 6.11 | Execution time for streamed RGB to grayscale conversion of 32 frames      | 118 |

|------|---------------------------------------------------------------------------|-----|

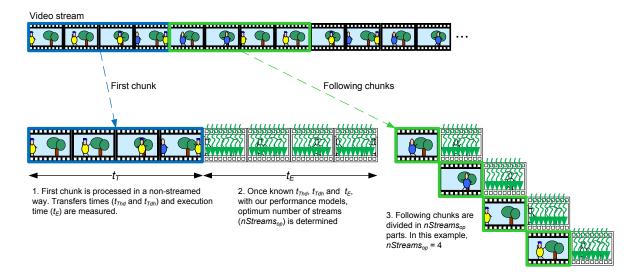

| 6.12 | Optimally streamed computation on a video stream                          | 119 |

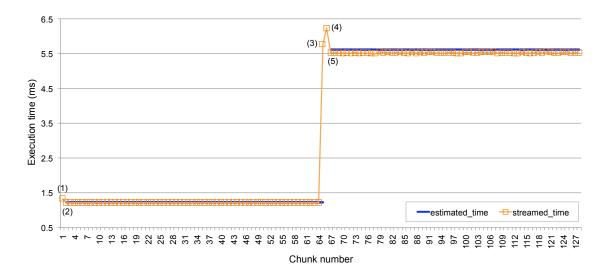

| 6.13 | Execution time for streamed 256-bins histogram computation of 4096 frames | 121 |

# **List of Tables**

| 2.1 | Hardware and software features in NVIDIA GPUs                                     | 22  |

|-----|-----------------------------------------------------------------------------------|-----|

| 2.2 | Hardware features of NVIDIA devices used in this dissertation                     | 22  |

| 3.1 | Summary of target applications and their parallelization problems                 | 44  |

| 4.1 | Experiments with atomic additions incurring in 2-way bank conflicts               | 58  |

| 4.2 | Recommended execution configurations on GeForce GTX 580                           | 71  |

| 4.3 | Average performance in GB/s of histogram calculation on GeForce GTX 580           | 75  |

| 4.4 | Average and minimum execution times for three histogram-based kernels             | 75  |

| 4.5 | Recommended execution configurations on GeForce GTX 280                           | 76  |

| 4.6 | Average performance in GB/s of histogram calculation on GeForce GTX 280           | 77  |

| 5.1 | Videos used for performance evaluation of a motion detection algorithm            | 87  |

| 5.2 | Implementations for search for pairings, scale and displacement calculations      | 95  |

| 5.3 | Test workloads characteristics for GHT implementation                             | 96  |

| 5.4 | Profiling of irregular kernels within the GHT                                     | 97  |

| 5.5 | Average execution times (ms) of the main parts of the application for four videos | 99  |

| 6.1 | NVIDIA GeForce Series features related to data transfers and streams              | 107 |

| 6.2 | Features of NVIDIA GeForce GPUs used in this work                                 | 112 |

| 6.3 | Values of $t_{sc}$ for devices from GeForce 8, 9, 200, 400 and 500 series         | 112 |

| 6.4 | Estimated and experimental optimal number of streams for three applications       | 117 |

| 6.5 | Number of frames per second for histogram calculation of a video sequence         | 121 |

# Video analysis on Graphics Processing Units

Video processing is a part of signal processing where input and/or output signals are video streams. It covers a wide variety of applications that are generally very compute-intensive due to the algorithmic complexity. Moreover, many of these applications demand real-time performance. Fulfilling these requirements makes necessary the use of hardware acceleration such as Graphics Processing Units (GPUs).

GPUs have spectacularly bursted in the scene of High Performance Computing (HPC) in the last few years, thanks to the advent of new programming models that allow an easy exploitation of their vast computing resources. They are successfully being used in an innumerable variety of scientific and engineering applications. Among them video applications are on the cutting edge of this revolution, because of their computational requirements and the wide spectrum of end users that increasingly demands them.

This chapter contextualizes the parallelization of video applications on GPU and establishes motivations and goals of this dissertation. Section 1.1 gives an overview of current matters about computer performance and parallelism. In Section 1.2 GPUs are introduced as programmable general-purpose processors. In Section 1.3 research efforts in video and image processing on GPU are reviewed. Moreover, motivations and goals of this dissertation are stated. Finally, Section 1.4 depicts the structure of this document.

#### 1.1 Introduction

The ever-increasing need for processing speed, together with the sudden braking in the evolution of single-core Central Processing Units (CPU) due to power consumption and thermic problems, has made the industry search for alternative and productive computing platforms. Until today there is no known alternative to parallelism for sustaining growth in computing performance. Parallelism, that was traditionally exclusive for *supercomputing applications* on large and expensive distributed-memory or shared-memory multiprocessors, has been extended to new *chip multiprocessor* (CMP)

or *multicore* architectures. The deployment of these new architectures on all types of computers, included desktop and mobile devices, highlights the need for parallel programming, in order to take advantage of the multiple processing cores.

The former issues are introduced in this section. Then, the recent evolution of parallel computing platforms is reviewed. Finally, several topics related to programming parallel platforms are discussed and parallel programming models are presented.

#### 1.1.1 Parallelism as the key for improving computer performance

In 1965 Gordon E. Moore [80] predicted the exponential growth of transistor density along the years. The so-called  $Moore's\ law$  states that the number of transistors that can be placed inexpensively on an integrated circuit doubles approximately every two years. Consequently, for the last half-century computers have been doubling in performance and capacity every couple of years. This uninterrupted growth has boosted the age of  $Information\ Technology$  (IT).

IT has transformed our works and lives: it helps to bring distant people together, enhance economic productivity, advance science, enable medical diagnoses and treatments, improve weather prediction, produce and deliver content for education and entertainment, coordinate disaster response... These are just samples of an endless list that have been made possible by sustained improvements in computer performance. In this way, there exists a *societal dependence* on growth in computing performance [31]. Moreover, it has arisen the expectation that such phenomenal progress will continue into the future. Every sector of the economy pursues more productivity, efficiency and innovation, which are only possible through technological advances that should be supported by computer performance.

The mentioned exponential growth on performance was based on a corresponding growth on processors clock frequency. By scaling down the size of the CMOS integrated circuits, the supply voltage was reduced, in order to allow the increase of clock speed with an affordable power consumption. However, the physical limits of this strategy were reached by 2003, so that increasing performance required increasingly expensive energy demands and heat-dissipation challenges. The sustained performance improvement of single-core CPUs was abruptly stopped.

Therefore, future growth in computer performance will not come from increasing clock frequency but from new designs including multiple processing cores that make parallelism available. Applications will continue to enjoy performance improvement whether their inherent parallelism is exploited, in order to allow multiple threads of execution to work cooperatively. Thus, this new context, that has been called the *concurrency revolution* [132], has hardware and software sides.

#### 1.1.2 Recent evolution of parallel hardware

The first response that microprocessor vendors gave to the slowdown in the growth of processor performance was to include more than one processor core in the same chip. Chip multiprocessors or multicore processors multiply the number of transistors within the same die while maintaining power constrains under control. Processor cores share the main memory (and possibly some cache levels)

Figure 1.1: Schematic of heterogeneous architectures: CPU in combination with GPU (a), linked by the PCI Express bus; CPU in combination with FPGA (b), linked by HyperTransport or QuickPath Interconnect; and Cell Broadband Engine Architecture, which includes CPU core and accelerator cores within the same chip

and, as single-core processors, they implement superscalar architectures that can include multithreading designs and  $Single-Instruction\ Multiple-Data$  (SIMD) extensions such as MMX and SSE. Current desktop processors include up to 6 cores while server processors have up to 12 cores.

Multicore processors allow some kind of coarse-grain program parallelism, but they do not satisfy applications including massive data parallelism. Such a necessity has favored the appearance of many-core processors, that consist of hundreds of simple scalar cores. The main exponent of this trend are GPUs, that are presented in Section 1.2.

Another alternative for applications acceleration are Field Programmable Gate Arrays (FPGA). They contain execution units embedded that can yield high performance, because they exploit locality and program their on-chip interconnects to match the data flow of an application. They ensure orders of magnitude performance improvement over microprocessors and less power consumption.

GPUs and FPGAs are used as accelerators in conjunction with a CPU, forming a *heterogenous* computing system [10], as it can be seen in Figure 1.1. Such combinations offer high peak performance and energy efficiency. The CPU executes sequential code, and the accelerator deals with parallel and specialized computation. Both parts are linked by some high-speed bus, as the PCI Express bus [110] in the case of GPUs, or QuickPath Interconnect [58] and HyperTransport [55] in the case of FPGAs.

Together with the former, the third trend in heterogeneous computing are heterogeneous chips as the Cell Broadband Engine Architecture [17]. It consists of one CPU core, called Power Processing Element (PPE), and eight accelerator cores, called Synergistic Processing Elements (SPE), as presented in Figure 1.1(c). A related concept is AMD Fusion [1], an integration of CPUs and GPUs within the same die.

In the near future, many alternatives are glimpsed: a number of different designs for different purposes are being developed. Intel and Altera are working in a microprocessor with integrated FPGA for embedded applications [67]. The Intel's Single-chip Cloud Computer [52] will be a many-core design including 48 processors with dynamic configuration of voltage and frequency to attain reduced power consumptions. On-chip accelerators specifically designed for highly specialized tasks (cryptography, compression, network security...) are opening a wide spectrum of possibilities [50].

#### 1.1.3 Parallel programming models

Together with designing and building parallel hardware, the challenge of parallelism is developing programs in a way that mainstream applications can be benefited. A successful exploitation of parallelism is subject to several factors [31]:

- The application under consideration must inherently have parallelism. Many computational

problems have independent tasks or process large data sets in which operations on each individual item are mostly independent.

- The parallelism must be identified by the programmer. If tasks are not entirely independent, the programmer should identify communication and synchronization between tasks.

- Parallelization must be efficient. The amount of work assigned to each processing thread should be similar, ensuring load-balancing. Locality should also be properly exploited, in order to minimize synchronization and communication overheads.

- The parallel program must be correct. Programmers should be aware of dependence among tasks, communication and synchronization issues, restrictions of the programming models... They should have *computational thinking* skills [146], i.e., the ability to formulate problems into computational models that can be solved efficiently by available computing resources.

Unfortunately automatic parallelization of sequential codes has not worked well in practice. Sequential programs expose inherent dependences that require an accurate program analysis to understand its potential behavior. In this way, many parallel programming languages and models have been proposed in the past several decades. Choosing the proper programming model mainly depends on the parallel machine.

The most widely used parallel programming models are the Message Passing Interface (MPI) [81] and OpenMP [102]. They can also be used in conjunction [114, 147]. On the one hand, MPI is used for scalable cluster computing. It is originally a model where computing nodes do not share memory, although it is also used in shared-memory machines [142]. All data sharing and interaction must be done through explicit message passing. MPI has been successful in the high-performance scientific computing domain, but the amount of effort required to port an application into MPI can be extremely high. On the other hand, OpenMP supports shared memory. Thus, it is successfully used for multicore processors allowing both data and task parallelism. However, it has not been able to scale beyond a couple hundred computing nodes due to thread management and frequent synchronization overheads [114]. In addition, certain types of parallelism have been more difficult to support in OpenMP. Examples are pipelining [35] due to complex synchronization needs, as well as client-server and nested parallelism that have benefited from the later introduced OpenMP tasking model [3].

Programming GPUs for general-purpose computations was extremely hard in the beginning, because standard graphics Application Programming Interfaces (API) were used. The Cg (C for graphics) shading language [84] was able to be used as a general programming language, thanks to basic data types and operators which work in a similar way to their C equivalents. Then, there were early attempts to provide general-purpose programming languages such as Brook [12]. Nevertheless, the

popularity of GPUs for general-purpose computations started with the advent of the Compute Unified Device Architecture (CUDA) [90] by NVIDIA. Since then, GPUs have demonstrated that they are a solid alternative for HPC applications.

In order to avoid the programming effort due to rewriting parallel programs for different platforms, several research works have tackled the translation of CUDA programs into OpenMP or vice

versa. MCUDA [130] allows CUDA programs to be executed on multicore processors. In [72] a

compiler framework for automatic translation of OpenMP applications into CUDA-based GPU applications is presented. That concern together with the fact that CUDA is only valid on NVIDIA

devices made several major industry players, including Apple, Intel, AMD/ATI and NVIDIA, jointly

develop OpenCL [65]. Similar to CUDA, OpenCL is a standardized programming model in which

applications can run without modification on all processors that support OpenCL. For instance, the

same OpenCL program can be executed on a NVIDIA GPU, an AMD GPU or a multicore processor.

Nevertheless, program optimization and tuning is very dependent on the hardware platform, so that

OpenCL is still far from being the definitive parallel programming model. Moreover, performance

comparisons between CUDA and OpenCL are nowadays clearly favorable to the first one [22, 25, 44].

In the case of FPGAs, programming is performed through hardware description languages (HDL) such as VHDL and Verilog. Hardware programming is hard and requires an advance expertise. An attempt to port CUDA programs into FPGAs is presented in [106]. A comparison between FPGAs and GPUs with CUDA and OpenCL can be found in [143].

Finally, there are several attempts in the industry to deliver higher-level data-parallel programming systems that allow certain kinds of data-parallel descriptions to be written once and then executed on different targets such as multicore, GPUs and FPGAs. Examples are Microsoft's Accelerator [133] and Intel Array Building Blocks [82]. Although these models do not ensure the best performance on the variety of target platforms, they might be sufficient for many classes of algorithms and users, and save a considerable programming effort [125].

### 1.2 Programming GPUs for general-purpose processing

In the eighties, graphics cards appeared as specialized processors for manipulating computer graphics. The term GPU was coined by NVIDIA in 1999 with the introduction of the GeForce 256, "The World's first GPU" [99]. It was technically defined as "a single-chip processor with integrated transform, lighting, triangle setup/clipping, and rendering engines". Such capabilities were based on a highly parallel structure that made them very effective while processing large blocks of data in parallel.

That massive computational power made some scientific researchers pay attention to the use of GPUs as general-purpose accelerators. Earlier works [46, 70] already noticed their potential performance. Nowadays, GPUs are a successful alternative for scientific and engineering applications, thanks to new architectural designs and new programming environments oriented to general-purpose computations, and the fact that there is a huge install base of desktop graphics cards.

There are two major GPU manufacturing companies, AMD and NVIDIA, and two booming programming models, CUDA and OpenCL. Latest AMD GPU, Radeon HD 6990M, promises a peak

performance of 1601.6 GFLOPs and a memory bandwidth of 115.2 GB/s while the most powerful NVIDIA GPU, GeForce GTX 580, has 1581.1 GFLOPs peak performance and 192.4 GB/s memory bandwidth. These figures sound impressive compared to current desktop CPUs, but real performance of an application is inevitably conditioned by the efficient exploitation of hardware resources. This section reviews relevant factors on GPU performance and suitable techniques for GPU programming. Although the following explanations are focused on CUDA and NVIDIA devices, they are also valid for OpenCL and AMD devices due to the similarities between both.

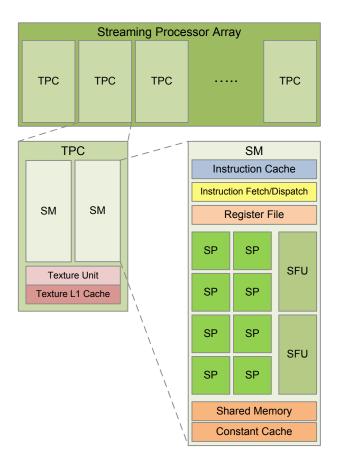

#### 1.2.1 A few words on CUDA

CUDA offers a huge number of threads (work items in OpenCL) running logically in parallel. Every thread executes the same code, called kernel, in a Single – Program Multiple – Data (SPMD) fashion. Threads are grouped into blocks (work groups in OpenCL) which are mapped to streaming multiprocessors (SM). A multiprocessor consists of several streaming processors (SP) which execute concurrently a collection of threads, called warp (wavefront in AMD GPUs). Warp size is 32 threads in current NVIDIA GPUs.

Multiprocessors have access to the same high-capacity off-chip global memory, their own low-latency on-chip shared memory (local memory in OpenCL), and a number of registers. On the one hand, the global memory bandwidth is used most efficiently when simultaneous memory accesses by threads can be coalesced into a single memory transaction. Coalescing occurs when the words accessed by all threads lie in the same memory segment. On the other hand, shared memory improves performance when data reuse exists. It is divided into banks which can be accessed simultaneously. The hardware also has cached constant and texture memories which are appropriate for read-only data.

An extensive introduction to CUDA programming model and hardware architecture is given in Chapter 2.

#### 1.2.2 Conditions and bottlenecks for GPU performance

In spite of the vast potential performance of GPUs and their improved programmability, achieving a significant performance is subject to some *conditions*. In order to harvest maximum performance benefits, the GPU formulation of an application algorithm should fulfill the following characteristics as far as possible [54]:

- Massive data parallelism: GPUs contain hundreds of execution units that perform properly when huge numbers of input data instances must be processed.

- Regularity in computations and data accesses: Threads should perform similar work.

- Avoidance of conflicts: The way memory bandwidth is exploited is crucial. Conflicting parallel accesses to memory locations are undesirable.

If the former conditions fail, the GPU implementation will suffer serious performance *bottlenecks* such as the following.

Serialization makes potentially concurrent threads be executed sequentially. Two are the main causes of serialization. On the one hand, kernels are SPMD programs where conditional branches can be included. These branches can provoke divergence among threads of the same warp. Each branch path taken is independently executed. On the other hand, certain memory accesses might result in contention between threads. Atomic operations in shared or global memory are serialized if different threads try to access the same location. Read or write accesses to shared memory are serialized as well when threads access more than one address in the same bank.

In general, the total amount of time to complete a parallel job is limited by the thread that takes the longest to finish. Typically, *load imbalance* appears with non-uniform data distributions.

GPUs have limited global memory bandwidth compared to peak compute throughput. This is able to provoke a memory-bound behavior of the application. In order to illustrate this, let us consider the peak throughput and memory bandwidth of GeForce GTX 580 given above. With 192.4 GB/s bandwidth, 48 G single-precision floating-point operands can be read per second. In order to achieve peak throughput (1581.1 GFLOPs), a program must perform  $\frac{1581.1}{48} \approx 32$  single-precision floating-point arithmetic operations for each operand. In this way, GPUs prefer high arithmetic intensity, that is, large amounts of instructions sequentially applied to the same operand [103].

#### 1.2.3 Generic optimization techniques on GPUs

Programmers should face many challenges when implementing GPU applications. Attaining the mentioned performance conditions might be a hard task. In the following lines a survey of optimization techniques applicable to GPU programming are reviewed [54, 119].

**Increasing locality in dense arrays** In many applications input data elements are accessed several times during execution. This data reuse can be effectively managed through the shared memory. *Blocking* or *tiling* technique consists of identifying chunks of global memory content that are accessed by multiple threads and loading them into shared memory, as depicted in Figure 1.2. Examples of the use of this technique can be found in several codes in CUDA Software Development Kit (SDK) [86] such as matrix multiplication and convolution.

Data reuse can also be managed through registers, that are even faster than the shared memory [140]. *Register tiling* is profitable when threads do not need to access data in registers owned by other threads.

**Improving efficiency and vectorization in dense arrays** Thread coarsening stands for how much work performs each thread. With this technique the work that would be assigned to multiple threads in a straightforward implementation is merged so that each thread calculates multiple output elements. In this way, possible redundant work is performed only once. Moreover, this technique increases Instruction Level Parallelism (ILP), which helps to hide pipeline latencies [141].

The merged code will result in the use of more registers probably causing a reduction in the ratio of active threads per SM (the so-called *occupancy*). Nevertheless, the increase in the ILP compensates for the reduction in Thread Level Parallelism (TLP). Figure 1.3 explains TLP and ILP approaches.

Figure 1.2: Blocking/tiling in shared memory. First, threads load chunks of global memory data into shared memory. This can be performed by coalesced accesses. Then, threads take advantage of data reuse in the faster shared memory

Figure 1.3: Thread Level Parallelism (TLP) vs. Instruction Level Parallelism (ILP). A TLP approach fills the pipeline with instructions from different warps. An ILP approach chains instructions from the same warp. The pipeline flows without stalls in both approaches, if the instructions that the warp scheduler launches are independent

**Reducing output interference** Many applications in GPU computing are easily designed by using a *scatter* approach, that consists of assigning one thread per input element, as shown in Figure 1.4 (left). Such an approach performs particularly well in highly regular and workload-independent computations. However, in some cases output elements are affected by more than one input element. Under such circumstances a scatter approach would suffer contention among threads. It should use atomic operations, which provoke serialization. Therefore, it is most beneficial assigning one thread per output element, i.e., a *gather* approach, as illustrated in Figure 1.4 (right). Examples of gather implementation are direct coulomb summation [128] and parallel reduction [43].

Figure 1.4: Scatter and gather parallelization. A scatter approach assigns one thread per input element. It suffers write contention when more than one thread access the same output element. In a gather approach one thread is assigned to one output element. An input element can be broadcasted when it is read by more than one thread

Nevertheless, in applications with a reduced number of output elements a gather approach makes no sense, because the reduced number of threads would be insufficient for exploiting the vast GPU resources. Hence, other optimization techniques must be found for improving the scatter approach. For instance, approaches to histogram calculation employ *replication* schemes in global or shared memory, in order to decrease contention [112, 123].

**Dealing with non-uniform and sparse data** Non-uniform or sparse data sets must be carefully analyzed and reorganized, in order to attain efficient implementations. In the case of sparse data, *compaction* can reduce the number of memory accesses and instructions executed, and the incidence of warp divergence [109]. Non-uniform data can be *sorted* by certain characteristics and divided into chunks or *bins* which can be loaded into shared memory. Moreover, parallel *prefix sum* or *scan* operations can be used to generate an array of starting points of all bins. *Sorting* and *binning* are successfully applied in cutoff summation [118] and MRI reconstruction [129].

The former techniques require fast implementations of parallel primitives, such as compaction, sorting and scan, that can be found in highly optimized libraries like CUDPP [21] and Thrust [8]. Another set of high performance parallel primitives was presented by Billeter *et al.* [9].

**Dealing with dynamic data** In some staged applications, usually referred to as wavefront, data to be processed in each phase of computation need to be dynamically determined and extracted from a bulk data structure. Such data must be organized for exploiting locality and coalescing, whilst contention is avoided. The amount of work and the level of parallelism often grow and shrink during execution. Examples are graph applications such as Breadth-First Search (BFS). Queue - based approaches and kernel - arrangement approaches have been successfully used in BFS. The former organizes dynamic data in a hierarchy of warp, block and global queues to carry out the algorithm phases [71]. The latter launches one kernel per phase with adaptive number of threads and blocks [76].

Figure 1.5: Global memory organization and addresses. Global memory is organized in DRAM channels/banks. *Steering bits* of global memory addresses decode DRAM channel and bank

Improving data efficiency in structured grids Applications such as Partial Differential Equations (PDE) solvers, in which data is arranged in *stencils* or other multidimensional *grids*, can be benefited from a two-fold optimization of global memory accesses. First, the data layout is transformed so that memory accesses from a (half-)warp are coalesced. Second, memory accesses across warps exploit Memory Level Parallelism (MLP), if warps are planned to access distinct DRAM channel and banks which form global memory. This can be achieved through certain *steering bits* of global memory addresses that decode the channel/bank [131], as illustrated in Figure 1.5.

## 1.3 Towards video processing optimization on GPU

Video processing encompasses compression, enhancement, analysis and synthesis of video streams. It is intrinsically related to image processing, because a video stream is a sequence of still images, called frames, representing scenes in motion. In order to achieve the illusion of a moving image, the minimum number of frames per second (fps), called  $frame\ rate$ , should be at least fifteen. Typical frame rates are 25 or 30 fps, although new professional cameras record 120 or more fps.

Nowadays, the ever-increasing amount of video and image data needs ever-increasing computational power. Images and frames resolution also tends to increase. Indeed, high-definition (HD) contents are getting more popular. In addition, video and image processing applications are computationally intensive and often present real-time or super-real-time requirements. For example, surveil-lance and monitoring systems need to robustly analyze video from multiple cameras in real time to automatically detect unusual events.

Luckily, video and image algorithms are highly amenable to parallel processing, because they exhibit data parallelism and strong computational locality. For instance, video tends to contain high degrees of locality in time (contents of one frame are similar to contents of previous or next frame) and in space (neighboring pixels have similar values).

In this regard, GPUs are becoming extensively used computing devices in today's video and image processing applications. GPUs are cheap, powerful and widely installed in consumer devices, while video and image processing is already demanded by more and more end users. Moreover, GPUs not only speed up video and image processing applications, but they also offer a vast computational power to transform the workflows themselves [53]. For example, GPUs perform filters and operators in real-time on full HD video, making low-resolution preview windows obsolete. Until now, many sophisticated video and image processing applications were executed off-line due to long latencies. The transitioning of these applications into real-time domain enables opportunities such as additional user interaction or more intelligent interactive tools.

While parallelizing video applications on GPU two main considerations have to be taken into account:

- Video applications should be properly mapped onto GPU resources. Many components of these

applications are inherently parallel, as frames are regular data structures and the same computation is typically applied to every pixel. However, parallelizing other components is pretty much

challenging, because of a variety of factors such as workload-dependent computations, use of

sparse or non-uniform data, etc.

- GPUs belong to a heterogeneous system. Video streams, which can be very long or even endless, should be transferred from CPU to GPU, and results from GPU to CPU. Such transfers constitute a performance bottleneck. The granularity of video data transfers and the consequent computation might have a significant impact on performance. The stream processing paradigm can help programmers to face this issue.

After reviewing the state of the art of video and image processing, this section discusses the former considerations. Then, aims of this dissertation are stated.

#### 1.3.1 State of the art of video and image processing on GPU

Since the advent of CUDA a huge number of video and image applications have been ported to GPU. A significant research work has been performed in many subjects such as image segmentation [139], feature detection [20, 149, 150], stereo imaging [23, 34], machine learning & data processing [15, 33, 73, 115], particle filtering [13, 79], optical flow [108, 144], and edge detection [77, 105, 108].

Most of the above works are focused on properly mapping algorithms onto GPU architecture. Systematic analysis and guidance generally applicable are scarce. In this way, a set of metrics customized for image processing are presented in [107]. The metrics, sorted by relative importance, are the parallel fraction (i.e., Amdahl's law [2]), branch diversity, per-pixel floating-point computation, per-pixel memory access, floating-point computation to global memory access ratio, and task dependency. They can be used for predicting the effectiveness of an application for GPU implementation.

In [74] several program optimizations applicable to video processing on GPU are evaluated. The authors use three-dimensional convolution as a pedagogical example. They present a baseline implementation, and then carry out subsequent optimizations such as the use of shared memory, streaming pattern and computation in Fourier domain. They also provide an overview of video applications such as video event detection, spatial interpolation, and depth image-based rendering.

Finally, several open-source libraries for image processing and computer vision such as Open-VIDIA [32], GPUCV [27], minGPU [4], and GPU4vision [57] have appeared. In addition, CUDA toolkit [89] provides the NVIDIA Performance Primitives library (NPP) [91] for image and video processing.

#### 1.3.2 Efficient mapping of video analysis applications on GPU

As it has been noticed, video applications are very suitable for parallel implementation and particularly GPU implementation. They are massively data-parallel, because frames are two-dimensional data sets which contain hundreds of thousands of pixels. Moreover, they typically implement complex algorithms which entail a large arithmetic intensity.

Most of these applications or at least many components of them are considered to be regular in the sense that they apply the same computation to every pixel. This inherent parallelism facilitates porting the application onto GPU and ensures:

- Load balancing: every thread will perform a similar amount of work.

- Linear addressing: consecutive threads will access consecutive addresses assuring locality of reference and coalescing.

- Avoidance of serialization: threads will follow the same execution path.

An example of regular computation is color conversion, for instance YUV to RGB [94]. A straightforward implementation which simply assigns one thread per pixel will yield a satisfactory performance. A more sophisticated implementation will be necessary to perform a convolution. In order to deal with data reuse, tiling in shared memory will be very profitable [74, 113].

However, parallelization becomes more challenging in some other components which should manage sparse or non-uniform intermediate data, present workload-dependence, or include sequential phases. In the following lines we identify different cases of irregular computation found during the development of this thesis. Under each bulleted item we draw one example and one possible solution:

- Write collisions that are unpredictable because of workload dependence. They should be resolved with atomic operations.

- This occurs in histogram computation.

- $\Rightarrow$  As mentioned in Section 1.2.3, replication alleviates contention [112, 123].

- Inherently sequential computations that underutilize GPU resources.

- Any iterative process with separated  $Single Instruction \ Single Data$  (SISD) and SIMD phases.

- $\Rightarrow$  Executing just one thread on the GPU might be more efficient than transferring data and computing on the CPU.

- Non-linear memory references that are due to workload-dependent memory accesses or unsuitable data organizations. They provoke uncoalesced accesses to global memory or bank conflicts in shared memory.

- Any operation in which threads should process the image by columns instead of by rows.

- $\Rightarrow$  In [30] image transposition enables linear accesses while applying the wavelet transform by columns.

- Load imbalance and warp divergence that are due to workload-dependent computations and/or

the handling of intermediate sparse, non-uniform, or dynamic data. They might cause serialization, and unproductive memory accesses and executed instructions.

- After a contour detection an edge image is a sparse data organization. Threads assigned to edge pixels will work, but the rest will remain idle while processing the edge image.

- ⇒ A compaction step can be applied in order to remove non-edge pixels.

#### Motivation

As it can be seen, attaining efficient implementations of irregular parts requires programmers to apply an additional effort which is indispensable for performance. Systematically tackling parallelization problems is necessary to consolidate GPUs as readily available high-performance platforms for video processing.

In this regard, this dissertation will focus on designing and applying programming strategies that lead us to achieve load balancing, linear addressing, and serialization avoidance while mapping those non-inherently parallel parts onto GPUs. Thus we direct our efforts to investigate:

- Improvement of histogram-based kernels by minimizing write contention. Current approaches to histogram calculation yield very far from peak performance. For instance, in [123] the authors reported throughput values under 11 GB/s on a GeForce 8800 GTX with 86.4 GB/s peak memory bandwidth.

- Proper mapping of SISD and SIMD phases by designing warp-centric approaches. A warp-centric implementation distributes data and computation among warps instead of blocks. In SISD phases some parallelism can be achieved, although one sole thread per warp works. Moreover, these implementations can avoid divergence and intra-block synchronization overheads by being conscious of warp behavior.

- Use of data-parallel primitives (compaction, sorting...), which re-organize input data, in irregular parts of video applications, in order to attain load balancing and linear addressing, and to avoid intra-warp divergence. A proper data organization also saves memory accesses and executed instructions.

- Evaluation of tradeoffs in load-balanced implementations. Since a perfect load balancing requires a more complex handling of data accesses and work distribution, it entails a more intense use of registers and shared memory that can burden the occupancy of multiprocessors.

#### 1.3.3 Stream processing paradigm for video analysis on GPU

In the last years, stream processing has become the preferable computer programming paradigm for certain classes of real-time applications such as video and other media processing applications.

Figure 1.6: Comparison between SISD (a), SIMD (b) and stream processing (c). SISD and SIMD executions apply a sequence of instructions to one single data element or multiple data elements respectively. Nevertheless, in the stream processing paradigm data is organized in streams and computation in pipelined kernels. The first kernel receives an input stream, intermediate kernels work with intermediate streams, and the last kernel outputs a resultant stream

Stream processing meets the computational demands of these applications on programmable architectures, avoiding the need for inflexible special-purpose solutions [63].

In this way, some specialized stream processors were designed for media processing [64, 117]. Nevertheless, a more recent trend is joining stream processing and GPU architecture.

#### Stream processing

The stream processing paradigm defines computation in terms of operations performed on sets of data elements or *streams*. Operations are grouped into *kernels*, so that each kernel processes an input stream and writes the results in an output stream. Kernels are usually pipelined. Figure 1.6 compares SISD, SIMD and stream processing paradigms.

Stream processing has been applied to disparate systems such as dataflow systems, reactive systems and signal processing [127]. These applications have in common certain characteristics [116]:

- Data parallelism: the same function is applied to every data element or record in a stream. Moreover, a number of records can be processed simultaneously without waiting the results from previous records.

- Arithmetic intensity: a high number of arithmetic instructions is typically applied to every input record.

- Data locality: records in a stream or streams themselves might be affected by neighboring counterparts but not by remote ones. This generates a regular and deterministic data flow in

which data elements are processed only once or a short number of times. Thus, pipelined kernels are able to work with independent streams.

#### Research efforts towards stream processing on GPU

Recently, several research works have tackled the adaptation of the stream processing paradigm to GPUs. They make use of the StreamIt programming model [134], which supplies programming constructs that raise the abstraction level of stream processing.

In [136] it is described a method to orchestrate the execution of a StreamIt program on a heterogenous platform with multicore CPU and GPU. This approach identifies the relative benefits of executing a task on the CPU and the GPU. The method formulates the problem of partitioning the work between CPU and GPU, taking into account the latencies of data transfers, as an integrated Integer Linear Program (ILP) which can then be resolved by an ILP solver.

A compilation framework for GPU using synchronous data flow streaming languages, called Sponge, is presented in [49]. Sponge performs a variety of optimizations to generate efficient code. It provides portability across different GPU generations thanks to a higher abstraction of hardware details.

In [41] an automated compilation flow that optimizes the mapping of stream processing applications on GPU is presented. This approach proposes the use of a mixture of memory access threads, which are in charge of copying data from global memory to shared memory, and compute threads, which are disconnected from global memory. The tradeoff between memory access and compute threads is determined by a heuristic that automatically selects the best mapping parameters.

#### **CUDA** streams

In CUDA a *stream* is defined as a sequence of commands that execute in order [97]. These commands can be data transfers or kernel launches. CUDA streams are announced as the way to overlap communication and computation. Since data transfers are an intrinsic performance bottleneck of GPUs, the use of CUDA streams alleviates it by hiding data transfers with execution. Moreover, the CPU can be performing other tasks concurrently, because CUDA streams use non-blocking (asynchronous) memory transfers. In Fermi devices [93] CUDA streams also allow concurrent kernel execution within the same GPU, and concurrent data transfers between CPU and GPU in Tesla devices.

#### Motivation

In this dissertation, CUDA streams are interpreted as the way to implement stream processing in CUDA. We focus on video processing applications, which exhibit the stream processing characteristics listed above. As indicated in Section 1.3.2, arithmetic intensity and data parallelism are respectively due to the algorithmic complexity and the massive number of pixels in each frame. Both are desirable features for GPU computing, as it was stated in Section 1.2.2.

Data locality is clearly reflected by the fact that video applications typically process single frames

or short sequences of frames in an independent manner. Thus, in a heterogenous CPU-GPU environment these (sequences of) frames can be independently transferred from CPU to GPU, processed in the GPU, and results transferred from GPU to CPU. Such a succession of events can be efficiently managed by CUDA streams with the added advantage of hiding data transfer latencies.

Let us consider a long or endless video stream that should be processed on a GPU. The video stream can be divided into chunks of a certain number of frames. Each chunk is assigned to one CUDA stream. Then, each CUDA stream will be responsible for transferring the chunk from CPU to GPU, applying computation through one or more kernels, and transferring the results from GPU to CPU. Synchronization of these steps will be automatically carried out.

We investigate the impact (if any) of the chunk size and the number of streams on performance, in order to obtain an optimum application of CUDA streams to video processing.

#### 1.3.4 Aims of this work

The main goal of this dissertation is obtaining efficient implementations of video analysis applications on GPUs. In this way, we tackle such a challenge from two sides, as it has been introduced above. First, we investigate proper mappings of video and image algorithms onto GPU, paying attention to memory access and work distribution. Second, we deal with GPUs as part of heterogenous systems and look at video applications from the stream processing point of view by using CUDA streams. Thus, we pursue the following concrete aims:

- Developing optimized histogram calculation on GPU by an exhaustive analysis of the performance of atomic operations.

- Dealing with inherently sequential parts (SISD) surrounded by massively data-parallel parts (SIMD).

- Achieving load-balanced implementations of irregular components of video applications after the use of data-parallel primitives which re-organize the workload.

- Evaluating the tradeoffs during the development of load-balanced implementations, which require a complex handling of data accesses and work distribution.

- Analyzing the behavior of CUDA streams and investigating how data transfers are overlapped with computations, in order to use them optimally.

- Designing an optimized scheme for stream processing on GPU based on CUDA streams.

#### 1.4 Structure of this document

This section explains how this document is organized. As a roadmap through the motivations of this dissertation, Figure 1.7 summarizes the main programming issues related to the parallelization of video applications.

6 Universidad de Córdoba

Figure 1.7: Programming issues for video analysis tackled in this dissertation. The yellow boxes represent the challenges that a programmer must face, while parallelizing irregular components in video applications. The green box stands for the application of the stream processing paradigm. It is indicated the chapter in which these issues are studied

Chapter 1 gives an overview of current issues in parallel processing and introduces GPUs as general-purpose processors. Then, it presents the goals and structure of this work.

Chapter 2 contains an extensive introduction to the CUDA programming model and hardware architecture. A thorough comprehension of these concepts is necessary to understand the rest of this document. Moreover, characteristics of NVIDIA GPUs used in this dissertation are presented.

In Chapter 3 three applications are presented, because they are conducting threads along the document. The first one is histogram calculation, a very common operation in video and image processing, that poses serious parallelization problems due to write contention. The other two are complete applications that have been chosen because of the variety of kernels they include that permit us to illustrate part of the aims of this dissertation.

Chapter 4 investigates proper techniques to avoid or minimize the negative impact of write contention. It performs an exhaustive analysis of atomic additions that conducts the design of an optimized approach to histogram calculation.

Chapter 5 deals with efficient work distribution within GPUs. Through several case studies presented in Chapter 3, this chapter proposes the use of warp-centric approaches to deal with sequential

phases, explains the use of data-parallel primitives to re-organized the workload and explores the tradeoffs of perfectly load-balanced implementations.

Chapter 6 studies the implementation of the stream processing paradigm by using CUDA streams. It proposes performance models for overlapping data transfers and computation and explains how to adapt the size and the number of streams automatically.

Finally, Chapter 7 presents the main conclusions and future research lines derived from this dissertation.

# An introduction to GPU computing with CUDA

In the beginning of the last decade, some pioneering researchers started to use Graphics Processing Units (GPU), which were traditionally oriented to graphics rendering acceleration, as general-purpose coprocessors. Although a promising trend, it was heavily burdened by a scarce programmability.

Taking a visionary initiative, NVIDIA launched the Compute Unified Device Architecture (CUDA) in February 2007, as the compute engine which makes the vast computing resources of GPUs accessible to every software programmer. In this way, NVIDIA GPUs have impressively arisen as a readily available alternative in High Performance Computing (HPC).

In this Chapter, main issues related to CUDA architecture and programming model are briefly reviewed. Section 2.1 explains the origins of GPU computing. CUDA-enabled devices are presented in Section 2.2. Section 2.3 depicts the CUDA programming model and Section 2.4 gives the hardware point of view. More detailed description about CUDA can be found in NVIDIA CUDA literature [93, 96, 97], and in some valuable teaching books [26, 66, 122].

### 2.1 Graphics processing units as general-purpose processors

Microprocessors based on a single Central Processing Unit (CPU) were evolving with rapid performance increases and cost reductions in computer applications for more than two decades. During this period, increasing the speed of applications was mainly delegated to the advances in hardware. Each new generation of processors ran faster than the previous. However, this trend has been abruptly slowed down since 2003 due to energy-consumption and heat-dissipation issues that have limited the increase of the clock frequency.

Consequently, microprocessor vendors have switched to models with multiple processing units, or *processor cores*, within the same chip. Two alternatives have arisen. On the one hand, *multicore* processors include two or more CPU cores. Each of them is an out-of-order, multiple-instruction issue processor. As their predecessors with a single CPU, they are designed to maximize the execution

Figure 2.1: Comparison of CPU and GPU architectures. CPUs include a few out-of-order processor cores and large caches. GPUs are devised to execute hundreds of threads in parallel and to achieve a high memory bandwidth

speed of sequential programs, while easing the cooperation between a short number of computing threads. On the other hand, many-core or  $massively\ parallel$  processors focus on the execution throughput of parallel applications. They have hundreds of small in-order cores. Main exponents of this trend are GPUs, which have experimented a spectacular revolution in terms of computing capabilities and programmability during the last five years.

These two types of processors present different design philosophies, as it is illustrated in Figure 2.1. Multicore CPUs include a sophisticated control logic to allow instructions from a single thread of execution to execute in parallel or even out of their sequential order while maintaining the appearance of sequential execution. Large cache memories are provided to reduce instruction and data access latencies. On the contrary, GPUs are able to execute many threads of execution in parallel and exhibit around 10 times higher memory bandwidth than CPUs. Such characteristics were originally oriented to boost the performance of 3D graphics visualization, but some researchers started to exploit them for general purpose computation in the early 2000s.

General-purpose program development on GPUs was extraordinarily convoluted in the beginning. Standard graphics Application Programming Interfaces (APIs), such as OpenGL or DirectX, were the only way to interact with a GPU. Thus, any attempt to perform arbitrary computations on a GPU was subject to the constrains of programming within a graphics API.

Those GPUs were designed to produce a color for every pixel on the screen using arithmetic units called  $pixel\ shaders$ . A pixel shader uses its (x,y) position on the screen as well as some additional input data to compute a final color. Since the arithmetic on such inputs was controlled by the programmer, these input colors could actually be any data. Valuable works applied such a new approach to general-purpose applications, such as matrix-matrix multiplication [28] or signal processing [36]. These incipient efforts were called General-Purpose GPU (GPGPU) programming [37].

GPGPU precedes the GPU Computing [38, 92] era, which is initiated with the introduction of CUDA by NVIDIA in 2007. The CUDA programming model has dramatically improved the programmability of GPUs by extending the C language to express parallelism. The model for GPU computing is to use a CPU and GPU together in a heterogeneous computing model. The sequential part of the application runs on the CPU and the computationally-intensive part is accelerated by the GPU. *Host* and *device*, i.e. CPU and GPU, are connected through a PCI Express bus [110], which

provides a peak of 16 GB/s. CUDA boosts this heterogenous model by allowing the overlap of data transfers and computations and, in recent devices, the concurrent execution of different functions on the device.

Nowadays, CUDA and the GPU computing model are being actively and successfully used in HPC applications from diverse fields, from astrophysical to financial [87]. Moreover, CUDA has inspired the development of the standardized Open Computing Language (OpenCL) [65], supported by Apple, Intel, AMD/ATI and NVIDIA. Although promising, OpenCL is still in its dawn. It is much tedious to use than CUDA and the speedup achieved is much lower. A translation tool between CUDA and OpenCL was presented in [44], and performance comparisons can be found in [22, 25, 44].

### 2.2 CUDA-enabled devices

Every NVIDIA GPU since the 2006 release of the GeForce GTX 8800 has been CUDA-enabled, that is, they have the CUDA hardware architecture and support the CUDA programming model. Anyway, a complete list of CUDA-enabled GPUs can be found in [85]. NVIDIA GPUs are classified into three brand names: GeForce are consumer GPUs, Quadro GPUs are specialized in professional visualization, and Tesla are for technical and scientific computing.

Architectures have evolved so far along three generations: G80, GT200, and Fermi. Although the underlying paradigm is the same for the three architecture generations, there are significant differences that are listed in the following subsections. Main features of the three generations are summarized in Table 2.1.

The architecture generation is represented by the *compute capability* (c.c.). This is defined by a major revision number and a minor revision number. Devices with the same major revision number have the same core architecture. Thus, G80 and GT200 devices are c.c. 1.x, and Fermi devices are c.c. 2.x. The minor revision number corresponds to an incremental improvement of the core architecture, including new features.

In this dissertation, NVIDIA devices belonging to all CUDA-enabled generations have been used in the experiments. They are listed in Table 2.2.

### 2.3 CUDA programming model

In this section, main concepts behind the CUDA programming model are introduced. CUDA C extends C by allowing the programmer to define C functions, called *kernels*, that are executed in parallel by *threads*.

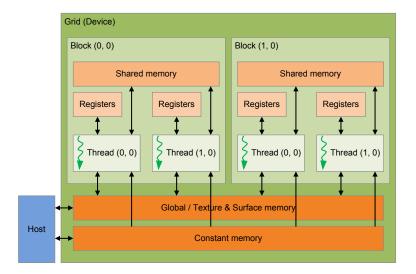

Kernels are called by the host thread. Kernel call syntax describes the *execution configuration*, which defines how threads are organized into a *grid* of *blocks*. Figure 2.2 summarizes the concepts presented in this Section.

### 2.3.1 Thread hierarchy

Threads are grouped into one-dimensional, two-dimensional or three-dimensional blocks. Within a block each thread is identified by its own  $thread\ ID$ , which is accessible through the built-in variable

Table 2.1: Summary of hardware and software features in NVIDIA GPUs. Comma-separated values correspond to different minor revision numbers

| Architecture                              | G80         | GT200       | Fermi          |

|-------------------------------------------|-------------|-------------|----------------|

| Compute Capability                        | 1.0, 1.1    | 1.2, 1.3    | 2.0, 2.1       |

| Transistors                               | 681 million | 1.4 billion | 3.0 billion    |

| Streaming Multiprocessors (SMs)           | Up to 16    | Up to 30    | Up to 16       |

| Streaming Processors (SPs) / SM           | 8           | 8           | 32, 48         |

| Special Function Units (SFUs) / SM        | 2           | 2           | 4, 8           |

| Warp Schedulers / SM                      | 1           | 1           | 2              |

| 32-bit registers / SM                     | 8192        | 16384       | 32768          |

| Shared Memory / SM                        | 16 KB       | 16 KB       | 48 KB or 16 KB |

| L1 Cache / SM                             | None        | None        | 16 KB or 48 KB |

| L2 Cache                                  | None        | None        | 768 KB         |

| Load/Store Address Width                  | 32-bit      | 32-bit      | 64-bit         |

| Memory Interface                          | 384 bits    | 512 bits    | 384 bits       |

| Threads / Warp                            | 32          | 32          | 32             |

| Threads / Block                           | Up to 512   | Up to 512   | Up to 1024     |

| Threads / SM                              | Up to 768   | Up to 1024  | Up to 1536     |

| Blocks / SM                               | Up to 8     | Up to 8     | Up to 8        |

| Overlap of data transfers and computation | No, Yes     | Yes         | Yes            |

| Concurrent Kernels                        | No          | No          | Up to 16       |

Table 2.2: Hardware features of NVIDIA devices used in this dissertation

| GPU          | Codename    | Compute capability | SMs / GPU | SPs / GPU      | Global memory             |

|--------------|-------------|--------------------|-----------|----------------|---------------------------|

| 8800 GTS 512 | G92-400     | 1.1                | 16        | 128            | 512 MB                    |

| 9600M GT     | G96         | 1.1                | 4         | 32             | 256 MB                    |

| 9800 GX2     | G92         | 1.1                | 2× 16     | $2 \times 128$ | $2 \times 512 \text{ MB}$ |

| GT 220       | GT216       | 1.2/1.3            | 6         | 48             | 512 MB                    |

| GTX 260      | GT200       | 1.2/1.3            | 27        | 216            | 896 MB                    |

| GTX 280      | GT200       | 1.2/1.3            | 30        | 240            | 1024 MB                   |

| GTX 480      | GF100       | 2.0                | 15        | 480            | 1536 MB                   |

| GTX 580      | GF110       | 2.0                | 16        | 512            | 1536 MB                   |

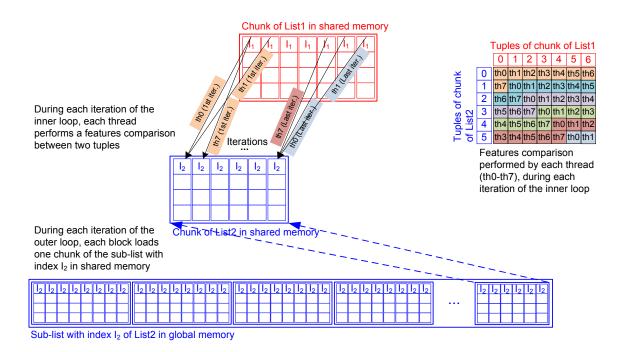

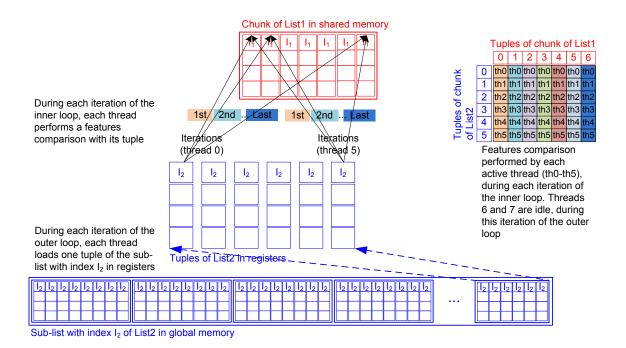

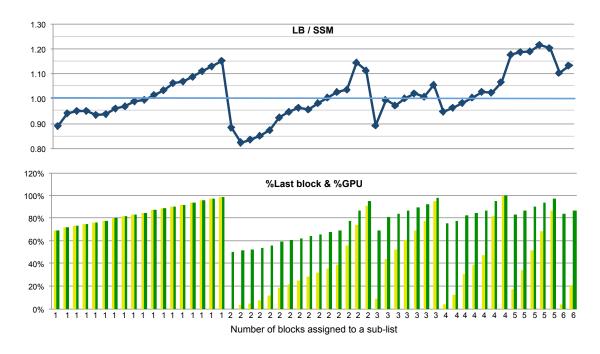

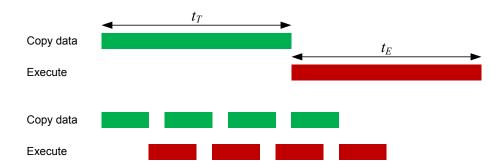

| C2050        | Fermi Tesla | 2.0                | 14        | 448            | 3072 MB                   |