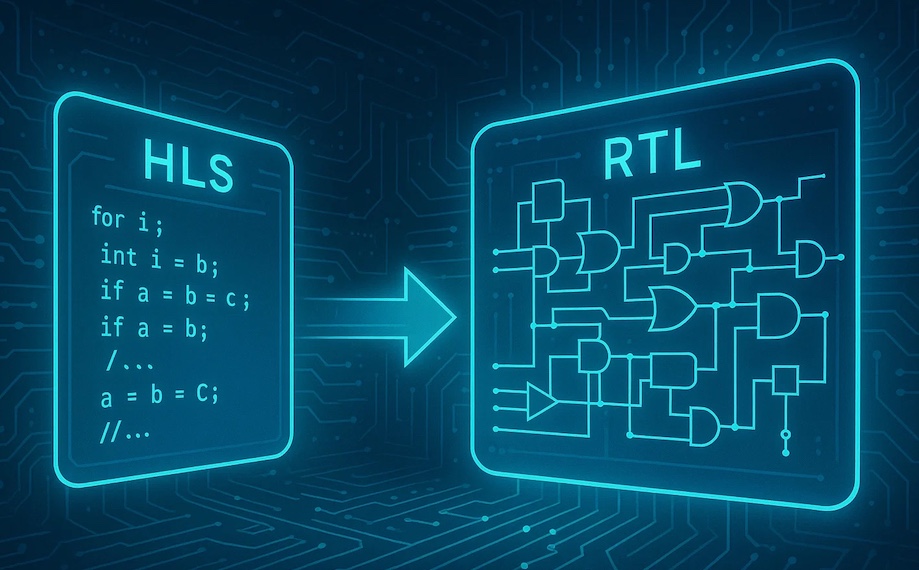

Ofrece una introducción a las herramientas de síntesis (RTL y HLS) para la generación automática de sistemas digitales complejos y su implementación en ASIC

Esta microcredencial ofrece una introducción a los fundamentos del lenguaje estándar SystemVerilog para su uso en descripciones hardware (RTL) de sistemas digitales. Estos sistemas abarcan desde las máquinas de estado finito, como unidades de control de procesadores a medida, hasta sistemas más completos que requieren de la integración de otros componentes digitales complejos, como, por ejemplo, bloques de memoria a medida de la aplicación. Por otro lado, se acelera la exploración de diferentes algoritmos de procesado a medida mediante el uso de herramientas de síntesis de alto nivel (HLS) y lenguajes de descripción de alto nivel, combinados con directivas de control del proceso de síntesis.

Con estas tecnologías se dota al alumno de las herramientas necesarias para el desarrollo productivo de sistemas digitales complejos para aplicaciones específicas (a medida).

Se aportan los conocimientos suficientes a los estudiantes para convertirse en excelentes profesionales en el campo de la microelectrónica, ayudando a satisfacer la creciente demanda de ingenieros especializados en semiconductores.

Tipo de enseñanza:

Esta microcredencial se realiza de manera online, esto es, en la modalidad virtual o remota.

Director académico:

Prof. Martín González García (Universidad de Málaga - Tecnología Electrónica), email: martin@uma.es

Objetivo concreto de esta microcredencial:

Introducción al diseño de sistemas digitales complejos mediante entornos de desarrollo automatizados basados en descripciones a nivel hardware (RTL) y lenguajes de descripción de alto nivel (HLS). La metodología propuesta permite crear nuevos sistemas considerando los diferentes niveles de abstracción para el diseño de sistemas basados en componentes digitales complejos, abordando aspectos críticos en el desarrollo a nivel de sistema.

Competencias o resultados de apredizaje:

Capacidad para modelar con HDL circuitos combinacionales y secuenciales.

Capacidad de integrar bloques digitales complejos en descripciones RTL.

Capacidad para diseñar procesadores a medida mediante metodología RTL.

Capacidad para diseñar y desarrollar el modelo de un sistema digital mediante HDL.

Capacidad para identificar potenciales problemas de cruce de dominio de reloj en el sistema a desarrollar.

Capacidad para modelar con lenguaje de alto nivel algoritmos para su síntesis HLS.

Capacidad para controlar resultados de la síntesis HLS mediante el uso de directivas/pragmas.

Contenidos de la microcredencial:

Fundamentos del lenguaje de descripción hardware estándar SystemVerilog y estilo de codificación.

Diseño secuencial utilizando SystemVerilog: máquinas de estado finito, como unidades de control, y unidades funcionales

a medida, como procesadores de datos.

Integración de componentes digitales complejos en descripciones RTL de sistemas digitales.

Fundamentos de la síntesis de alto nivel (HLS).

Exploración del espacio de diseño con HLS: pragmas.

Proyecto: Diseño de un sistema complejo usando herramientas RTL y HLS.

Equipo docente:

Prof. Martín González Garcia (Universidad de Málaga - Tecnología Electrónica)

Prof. Javier Hormigo Aguilar (Universidad de Málaga - Arquitectura de Computadores)

Número de créditos: 3 ECTS (30 horas)

Fecha de inicio: 20/04/2026

Fecha de fin: 26/06/2026

Horario:

Jueves, 17:30 a 20:30 (3 horas)

Lugar:

Campus Virtual, Microsoft Teams

Las actividades formativas tienen un marcado carácter práctico. Se hace uso de lecciones magistrales online para presentar fundamentos teóricos que se alternan con sesiones prácticas de laboratorio remoto donde se desarrollan el diseño de ejemplos de aplicación de los conceptos estudiados.

Al completar la microcredencial los estudiantes deben ser capaces de usar el lenguaje SystemVerilog para la descripción y desarrollo de sistemas digitales complejos, y el uso de herramientas de síntesis de alto nivel, para desarrollar algoritmos complejos a medida.

Evaluación de la formación:

La evaluación es continua y se realiza a partir del trabajo y los resultados obtenidos en cada una de las prácticas propuestas, cada una con un peso equivalente en la calificación final.

Titulaciones requeridas:

Ingeniería en Telecomunicaciones o afín (Telemática, Sistemas Electrónicos, Tecnología de Telecomunicación...).

Ingeniería Informática o afín (Computadores, Software...).

Ingeniería Industrial o afín (Electrónica Industrial, Mecatrónica, Robótica...).

Otras ingenierías afines.

Se admiten estudiantes de alguna de las titulaciones anteriores con estudios sin finalizar que tengan pendientes menos de 30 ECTS sin incluir el TFG y prácticas externas.

Los contenidos de esta microcredencial están relacionados con los de la microcredencial Laboratorio de Diseño de Circuitos VLSI Optimizados (Módulo 2).

Oscar Plata González

oplata@uma.es

M. Angeles González Navarro

magonzalez@uma.es

Departamento de Arquitectura de Computadores

Universidad de Málaga

29071 Málaga

©