# Productive interface to map streaming applications on heterogeneous processors

Andrés Rodríguez\*, Antonio Vilches\*, Angeles Navarro\*, Rafael Asenjo\*, Francisco Corbera\*, Rubén Gran<sup>†</sup>, María Garzarán<sup>‡</sup>

\* University of Malaga, Spain. E-mail: {andres, avilches, angeles, asenjo, corbera}@ac.uma.es † University of Zaragoza, Spain. E-mail: rgran@unizar.es

<sup>‡</sup> Dept. Computer Science, UIUC, USA. E-mail: garzaran@illinois.edu

#### Abstract

Current commodity processors include several cores and hardware accelerators, such as Graphical Processing Units or GPUs. These architectures pose two main challenges: i) determining how to map the application tasks to the computational device that maximizes performance and minimizes energy consumption; and ii) easing the programming interface so that the user productively exploits the heterogeneous architecture without dealing with low level details.

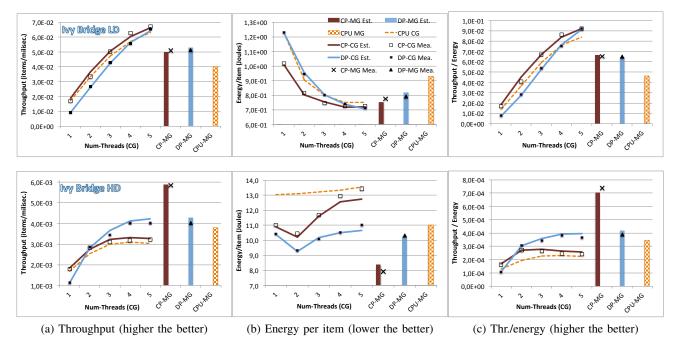

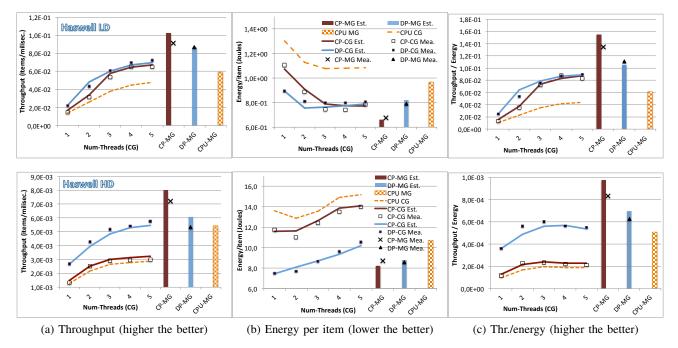

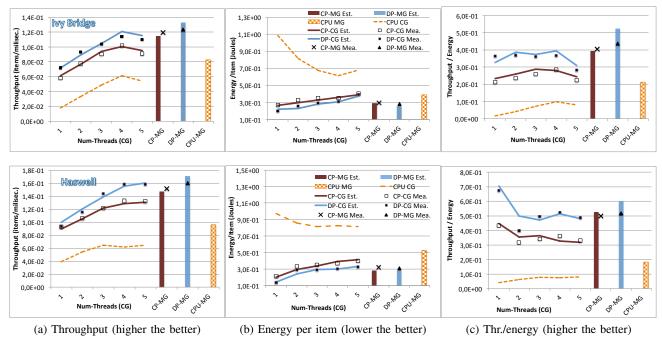

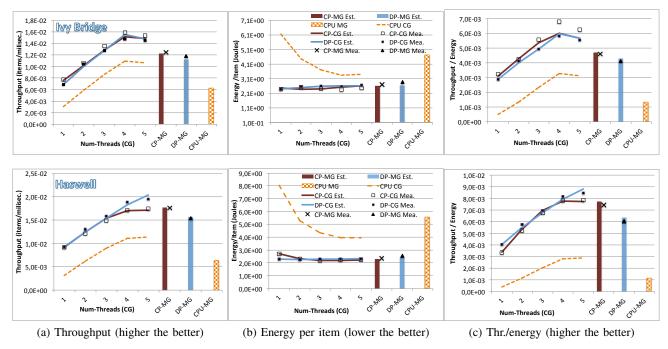

In this paper, we consider the problem of efficiently executing streaming applications on commodity processors composed of several cores and an on-chip GPU. Streaming applications, such as those in vision and video analytic, consist of a pipeline of stages and are good candidates to take advantage of this type of platforms. We also consider that characteristics of the input may change while the application is running. Therefore, we propose a framework that adaptively finds the optimal mapping of the pipeline stages. We describe the proposed API based on C++ templates that hide the underlying TBB implementation. The core of the framework is an analytical model coupled with information collected at runtime used to dynamically map each pipeline stage to the most efficient device, taking into consideration both performance and energy. Our experimental results show that for the evaluated applications running on two different architectures, our model always predicts the best configuration among the evaluated alternatives, and significantly reduces the amount of information that needs to be collected at runtime. This best configuration has, on the average, 20% higher throughput than the configuration recommended by a baseline state of the art approach, while the ratio throughput/energy is 43% higher. We have measured improvements in throughput and throughput/energy of up-to 82% and 204%, respectively, when the model is used to adapt to a video that changes from low to high definition.

#### **Index Terms**

Heterogeneous CPU-GPU chips, pipeline pattern, adaptive mapping, analytical model, energy aware.

#### I. MOTIVATION

Recently, we have seen a significant increase in the number of commodity multicore processors that include an on-chip GPU. Current desktops, ultrabooks, smartphones, tablets, and other embedded devices are powered by heterogeneous chips that comprise 2 to 8 CPU cores along with an integrated GPU. Examples of these are Intel Ivy Bridge and Haswell architectures, AMD APU, Qualcomm Snapdragon 800 and Samsung Exynos 5 Octa, to name a few. These heterogeneous chips can deliver significant speedups and low energy consumption compared to CPU-only systems on a large range of applications. However, issues such as the development of a suitable programming framework and runtime support for these architectures are in their infancy.

Most research in frameworks aimed at scheduling tasks on heterogeneous architectures, composed of CPU's and GPUs, has focussed on optimizing execution time without considering energy consumption [1], [2], [3], [4], [5]. However, a CPU core and a GPU exhibit different performance/energy trade-offs, this is, a workload can run faster on one device but consume less energy on the other one. Thus, in order to benefit from the potential energy efficiency that the accelerators can provide in these heterogeneous chips, the runtime scheduler also needs to consider the performance/energy asymmetry when making a scheduling decision [6].

In this paper, we focus on the problem of efficiently executing single streaming applications implemented as a pipeline of stages that run on heterogeneous chips comprised of several cores and one on-chip GPU, taking into consideration both performance and energy. Streaming applications are very common in today's computing systems, in particular mobile devices [7] where heterogeneous chips are the dominant platforms. To tackle the aforementioned problem, we study different choices such as: i) the granularity level at which the parallelism of each stage can be exploited (coarse or medium grain), ii) the mapping of the pipeline stages to the different computational devices and iii) the number of cores for which the application scales up. Our aim is to find the optimal configuration that considers all the previously mentioned factors. The metric to optimize can be throughput, energy or a tradeoff metric such as the ratio throughput/energy. We also consider that the best configuration may change over time. This can happen because the number of operations performed by each pipeline stage changes. There are several reasons why this can take place. For instance, YouTube, Skype Video [8], or tele-operated robots [9] adjust the resolution of the video stream based on the bandwidth of the network connection. Also, the computation of a pipeline stage may depend on the characteristics of the input frame. In this situation, an off-line training may not be feasible, as the best configuration will depend on the runtime input.

As a motivating example to demonstrate the benefits of adapting the configuration of a pipeline we introduce ViVid<sup>1</sup>, an application that implements an object (e.g., face) detection algorithm [10] using a "sliding window object detection" approach [11]. ViVid consists of 5 pipeline stages from which the first and the last one are the Input and Output stages. When applications like ViVid run on a heterogeneous on-chip architecture, many possible configurations are possible. To determine the best configuration, one needs to consider the granularity or number of items that should be simultaneously processed on each stage, the device where each stage should be mapped, and the number of CPU cores that minimize the execution time, or the energy consumption, or both. As we will discuss in Section VI, we have found that when ViVid runs on an Intel Ivy Bridge platform (also presented in Section VI), the best configuration for videos with Low Definition (LD) is different from the best one for videos with High Definition (HD) and not adapting to a input change, can have a significant impact in both, execution time and energy. For instance, when the video resolution changes from LD to HD, not changing from the best configuration for LD to the new optimal for HD results in 0.55x of throughput loss (and 1.7x of more energy used). On the other hand, if we are using the optimal configuration for HD, an input change from HD to LD will result in a 0.76x of throughput degradation (and 1.1x of more energy used) if we do not change to the new best configuration. These results indicate that an approach that can predict the best configuration, out of all the possible ones, is desirable. This approach should have low overhead, so that it can be used when an input change is detected.

In this paper, we propose an adaptive framework that can dynamically adjust the configuration of the pipeline (granularity, mapping and number of cores). This framework is based on an analytical model that, by collecting a small number of runtime experiments (only 8 on a quad-core), can predict the optimal pipeline configuration. Our framework can be targeted at optimizing performance, or energy or a tradeoff metric that considers the ratio throughput/energy. Our analytical model can provide knobs so that the user can specify a desired throughput or power budget. For instance, if the user specifies a throughput of 33 fps for realtime video streaming, the model can determine among the possible pipeline configurations, the one that minimizes the energy consumption and satisfies the user constraint. Similarly, given a power budget, the model can determine the fastest configuration. The information collected using runtime input data are used to dynamically adapt to input changes. Since this data collection phase can add some runtime overhead, our framework provides another knob so that the user can specify a threshold to limit the maximum overhead of this phase. We have evaluated our model using a set of streaming applications from vision and video analytic domain that are representative of the algorithms [12] that can benefit from the execution on these heterogeneous chips.

The contributions of this paper are the following ones:

- A taxonomy of the pipeline configurations for heterogeneous chips (section II).

- An adaptive framework that dynamically selects the best configuration while keeping the runtime overhead below an user-defined limit (section IV).

- An analytical model that quantifies how the different implementation factors interplay. This model can be used to predict the optimal granularity and mapping of the pipeline stages to the different computational devices, as well as the appropriate number of threads (section V).

- An evaluation of the accuracy of our analytical model. Our results demonstrate that the model accurately predicts, among the evaluated alternatives, the best pipeline configuration for all the applications and architectures studied (section VI).

# II. PIPELINE IMPLEMENTATION ALTERNATIVES

We use two axes to classify the different alternatives: (1) granularity level, that represents the level at which the parallelism is exploited on the CPU; and (2) pipeline mapping, that represents where the different

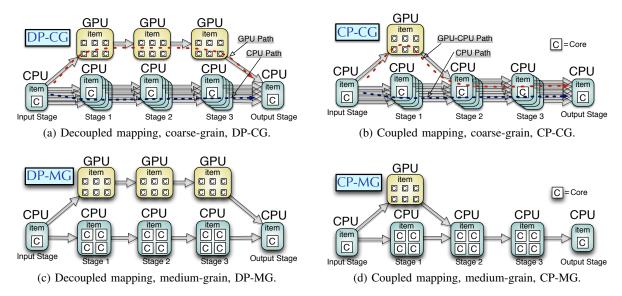

Fig. 1: Examples of the four different configurations for ViVid.

stages of the pipeline can execute. We call pipeline configuration to each possible combination of granularity and mapping. Fig. 1 graphically depicts examples of the 4 possible configurations for the ViVid pipeline on an Ivy Bridge-like architecture with a GPU (6 computing units) and a CPU multicore (4 CPU cores). The figure shows the paths that traverse the in-flight items being processed. The pipeline stages are represented as rounded rectangles, while the device (GPU or CPU) on which each stage is processed, is depicted with the number of computing resources (small squares with the letter 'C') that collaborate on the computation of each item.

**Granularity level**: The vertical axis in Fig. 1 classifies the approaches based on the granularity level used to exploit parallelism on the CPU. Two levels of granularity are considered: Coarse Grain (CG) and Medium Grain (MG). If different items can be processed simultaneously on the same stage (the stage is parallel or stateless<sup>2</sup>), CG granularity can be exploited. On the other hand, if the stage exhibits nested parallelism (which can be exploited by using OpenCL, OpenMP or TBB parallel\_for), then a single item can be processed in parallel by several cores in the CPU, and MG granularity can be exploited. The CG granularity is shown in Figs. 1a and 1b, where, on the CPU multicore, each item is processed by a single core (one thread). MG granularity is shown in Figs. 1c and 1d. In this case, a single item is processed in the CPU multicore, with each core (or thread) processing a portion of the item.

GPUs are not as flexible as the multicores regarding the granularity level of parallelism they can exploit. They excel at exploiting SIMT (Single Instruction Multiple Threads) type of parallelism. Thus, stages mapped onto a GPU only process a single item, with all the GPU processing units computing a portion of the item (similar to MG granularity, but at a finer grain).

The MG granularity requires a barrier synchronization after each pipeline stage and before the next pipeline stage can start, to guarantee that all threads have finished processing the item. Therefore, MG can hurt performance when the load is imbalanced or there is not enough computational load per core. With MG, it is like having two devices, GPU and CPU, that can only work on two different items at a time. Thus, there is less pipeline parallelism when exploiting MG granularity. However, with the CG granularity, each CPU core (or thread) can process all the pipeline stages for a given item without intermediate synchronizations, i.e. each item traverses the pipeline at its own pace. Two drawbacks of the CG approach are that several items are in-flight at the same time, which increases the memory pressure, and that it only applies to parallel pipeline stages. Finally, notice that each CPU core can also exploit fine grain parallelism, due to the vector units of the processors. This can be exploited by both, CG or MG granularities.

**Pipeline mapping**: The horizontal axis in Fig. 1 classifies the configurations based on whether all the stages execute on the GPU or only a few do. The first pipeline mapping is called decoupled (DP), while the other one is called coupled (CP).

Disregarding the Input/Output stages, DP mappings are illustrated in Figs. 1a and 1c, where we depict two

$<sup>^{2}</sup>$ A stage is parallel or stateless when the computation of an item on a stage does not depend on other items.

"decoupled" paths: i) a GPU path, in which a thread (the GPU thread) offloads all stages to the GPU for processing one input item; and ii) a CPU path, in which a group of concurrent threads (the CPU threads) process all stages on the CPU. On the other hand, CP mappings are shown in Figs. 1b and 1d where we see two paths that are not independent: i) a GPU-CPU path in which a thread (the GPU-CPU thread) offloads some stages to the GPU (stage 1 in the figures) for processing one input item, while the remaining stages are executed on the CPU; and ii) a CPU path, in which a group of concurrent threads (the CPU threads) process all stages on the CPU multicore. The difference between the CP's GPU-CPU thread and the DP's GPU thread is the following. In a CP mapping, when an item reaches the stage for which it has been decided that it will be processed on the GPU (stage 1 for the ViVid example), we first check if the GPU is idle, and in that case the thread becomes a GPU-CPU thread that launches the item's kernel to the GPU and then waits for the GPU kernel to finish. Then, the same thread also processes the item through the remaining stages (in the example, stages 2 and 3 that are processed in the CPU). However, in DP, when an item reaches the first stage and finds the GPU is idle, the corresponding thread becomes a GPU thread that processes the item throughout all the stages on the GPU. Indeed, when we consider only 1 thread for the DP mapping, that thread becomes the GPU thread and therefore all the items traverse the GPU path. This is what we call a GPU homogeneous execution. In our example, for both CP and DP, if an item on the stage 1 finds that the GPU is already busy, then the item is directed through the CPU path. Although DP could be seen as a particular case of CP where all the stages happen to be mapped to the GPU, we distinguish both mappings because they have to be modelled differently as we will see in section V.

CP mappings can be a good alternative when not all the stages are suitable for the GPU, or because it's not advisable to divert the GPU computing power from the stages where it is faster and/or more energy-efficient. This approach also has the advantage that not all the stages have to be implemented for the CPU and GPU. However, in the CP mapping, the GPU-CPU thread must orchestrate the "coupling" of the GPU and the CPU devices and the host-to-device/device-to-host communications, which results in some data movement and synchronization overheads. Also, note that DP mappings can be implemented only if all stages are parallel pipeline stages (stateless). If, on the contrary, all stages are serial, heterogeneity can be exploited by mapping some stages on the GPU and the rest on the cores, which is a particular case of the CP mapping in which all items are directed through the GPU-CPU heterogeneous path.

# A. Alternatives not considered

Some additional alternatives not considered in this classification are the following:

- Splitting an item to be simultaneously computed on the CPU and GPU. As it was demonstrated by Totoni et al. [13], this possibility is not beneficial for our vision applications due to additional synchronization overheads between both devices.

- Having one stage exploiting both MG and CG granularities on the CPU. For example, a quad-core can be splited into two CPU devices with two cores each. This approach would combine CG and MG on the same stage: two CPU devices processing two items in parallel (CG), and each item running on two cores (MG). For that, we explored the OpenCL Device Fission function (cl\_ext\_device\_fission) that can divide the CPU device into several subdevices with lower core count. However, we discarded this alternative for the following two reasons. On the first hand, we have measured 14% of overhead (for ViVid on Ivy Bridge) if the device\_fission is called to change the subdevices configuration from one pipeline stage to the next one. Thus, this approach is beneficial only if the optimum number of cores per device coincides for all the pipeline stages. On the second hand, the current OpenCL driver for Windows (there is no such a driver for Linux), relies on a busy waiting mechanism where the host thread has to wait for the kernel to finish on the corresponding subdevice. This means that for two CPU subdevices, two additional threads doing busy-wait will occupy two CPU cores, which results in further degradation of the execution time.

- Exploiting stages with both MG and CG granularities on the GPU. The OpenCL fission feature is currently not able to split the GPU on Intel or AMD heterogeneous chips. Therefore, we do not consider this feature to evaluate additional pipeline configurations.

- Hybrid mappings in which some CPU stages exploit MG and the rest CG granularity. This is left for future work.

# B. Accounting for all pipeline alternatives

Let's assume we have nC CPU cores (4 in Fig. 1), and 1 GPU in an heterogeneous chip (current commercial heterogeneous chips only contain a single GPU, so we overlook configurations with two or more GPUs in

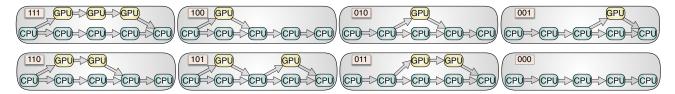

Fig. 2: All considered mappings of pipeline stages to CPU and/or GPU for ViVid.

this work). We've seen we have 4 pipeline configurations, DP-CG, DP-MG, CP-CG and CP-MG, but there are two additional factors to consider: i) for CP mappings we have to find out the stages for which the GPU is more profitable; and ii) for the CG granularity we also have to explore the optimal number of threads. For this CG granularity the number of threads in the CPU multicore can go from 0 to nC. Additionally, since the GPU thread in DP-CG, or the GPU-CPU thread in CP-CG, will be mainly hosting the GPU (waiting for the GPU task to complete), the total number of threads, n, we explore goes from 1 to nC + 1. This means that we allow oversubscription of one thread when n = nC + 1, and therefore, the GPU (or GPU-CPU) thread eventually interferes with the other nC CPU threads. For the MG granularity, we always configure nC + 1 threads because the constructors used to exploit nested parallelism (OpenCL or TBB parallel\_for) by default use all the threads available in the multicore, nC, plus the GPU (or GPU-CPU) thread.

With all that, assuming that the pipeline consists of s parallel stages, there would be  $2^s$  possible GPU/CPU mappings (this is illustrated in Fig. 2 for ViVid with s = 3). These mappings can be combined with nC + 1 different CG options, depending on the number of threads used and 1 MG option, i.e., nC + 2 options. Thus, in total we have  $2^s \cdot (nC + 2)$ . That results in 48 alternatives for ViVid with s = 3 and nC = 4.

Our goal is to be able to predict the optimal pipeline configuration specifying the granularity, mapping (identifying the stages that should be mapped on the GPU), and the optimum number of threads for a given stream input. But first, the general framework is presented.

# III. PROGRAMMING INTERFACE

In this section we introduce our pipeline library API. It provides a C++ programming environment that facilitates the configuration of a pipeline by hiding the underlying TBB implementation and by automatically managing the memory data transfers between devices.

The interface has four main components:

- Items: objects that traverse the pipeline carrying pointers to the data buffers.

- Pipelines: the pipeline itself is composed of s + 2 stages. We assume that it contains stages  $S_{in}$ ,  $S_1$ ,  $S_2$ , ...,  $S_s$ ,  $S_{out}$ , being  $S_{in}$  and  $S_{out}$  the serial Input and Output stages. Pipelines can be configured statically or run in an adaptive-configuration mode. This adaptive-configuration mode is the one that uses our proposed model to dynamically compute the best configuration and to adapt to input changes.

- Stage functions: each processing stage needs to be programmed to run on CPU and/or GPU. The pipeline uses the appropriate function for every stage.

- Buffers: n-dimensional arrays that can be used by both, the host code and the OpenCL kernels.

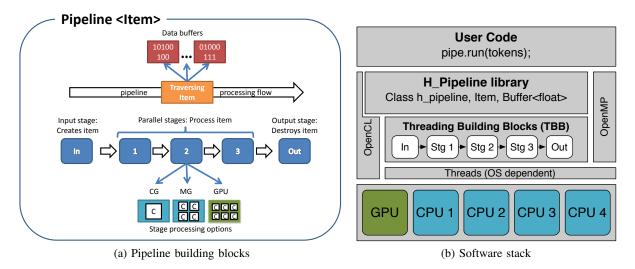

Fig. 3a shows all components involved in the pipeline operation. The Item is the object that traverses the pipeline. It contains the references to the data buffers that the different processing stages of the pipeline use as input and output. To create a new pipeline instance, the user needs to declare a new Item subclass (it must extend from a provided Item class) that should contain the references to data buffers used by the pipeline stages. For data buffer management, there is a DataBuffer<T> template class already defined, that hides all the important operations like allocation, deallocation, data movements, Zero-Copy Buffer mappings, etc. The aim of this data buffer class is to make the data accessible to the device (CPU or GPU) where the item has to be processed. Fig. 3b shows the hardware layer with the heterogeneous devices at bottom. On top of that, the middle layers (TBB, OpenCL, OpenMP) provide different programming models to exploit parallelism on the heterogeneous chip. However, we partially hide the details required by these low level libraries by providing a simpler interface based on C++ clases and templates.

The programmer can provide up to three different functions for every stage of the created pipeline: one to implement the stage on the GPU device using OpenCL, a second one to implement the stage on a single CPU core (CG granularity), and the third one to implement the stage on multiple CPU cores (MG granularity). The implementations not provided (CP, MG, and/or GPU) will not be considered when searching for the best pipeline configuration.

Let's see the components in more detail.

Fig. 3: Pipeline building blocks and software stack.

#### A. Item class

Fig. 4 shows a code snippet for the Item class declaration used in the ViVid pipeline. First, our pipeline interface is made available by including the h\_pipeline.h header file (line 1) . It also defines the h\_pipeline namespace which contains all the classes of the interface. As previously mentioned, before creating the pipeline, the programmer must define an Item subclass that will traverse the pipeline (line 7). The item class must extend from h\_pipeline::Item and declare as many DataBuffers<T> members as needed for the pipeline execution. The class constructor and destructor methods must hold the buffers creation and deletion, respectively. Alternatively and to avoid too many operations of buffer allocation/deallocation, a pool of buffers can be used. In that case, acquire and release methods can be invoked so that the same buffers are reused by different items. The Input and Output stages (i.e. the first and last serial stages of the pipeline,  $S_{in}$  and  $S_{out}$ ) automatically call the constructor and destructor of the Item class, respectively. In the last part of this section we will show an example of buffer usage (Fig. 7).

```

#include "h_pipeline.h"

// Required clases defined here

1

2 using namespace h_pipeline;

// New namespace

3

4

* 1.- ITEM Class (holds the data that traverse the pipeline stages

5

6

7 class ViVidItem : public h_pipeline::Item {

public:

8

//Buffer definitions

DataBuffer<float> *frame; // Input buffer

10

11

. . .

DataBuffer<float> *out; // Output buffer

12

13

14

//Constructor definition. Allocation or buffer acquire

15

ViVidItem() {

//Data Buffer allocation

16

17

. . .

18

//Destructor definition. Deallocation or buffer release

19

~ViVidItem() { ... }

20

21

};

```

Fig. 4: Using the Item Class.

# B. Pipeline

Fig. 5 shows a pipeline definition and usage example. After declaring the ViVidItem as shown in Fig. 4, we can create a new pipeline using that class (line 6) passing as constructors arguments the number of threads, numThreads, that will run the pipeline in parallel. In this study we set as maximum number of threads nC+1,

being nC the number of CPU cores (see section II-B). Notice also that the CPU (CG and MG granularity) and the GPU functions of the three stages for the ViVid example need to be set up before the pipeline can run (see lines 9 to 11). In case we want to run the pipeline using a static configuration, we use specific methods to configure some aspects of the pipeline, such as the stages that should map to the GPU or the granularity (MG or CG) that should be used in the CPU (line 14). In our example, in line 14, parameter  $\{1, 1, 1\}$  represents the s-tuple that express the mapping of stages to the devices (we will define it next) and the last argument, USE\_MG, indicates that MG granularity will be exploited when an item is processed on the CPU.

As mentioned before, we assume that a pipeline consists of  $S_{in}$ ,  $S_1$ ,  $S_2$ , ...,  $S_s$ ,  $S_{out}$  stages (s+2).  $S_{in}$  and  $S_{out}$ , the serial Input and Output stages will be always mapped to the CPU. For any other stage  $S_i$  such that  $1 \le i \le s$ , we use a s-tuple to specify all posible stage mappings to the GPU and the CPU devices:  $\{m_1, m_2, \ldots, m_s\}$ . The i-th element of the tupla,  $m_i$ , will specify if stage  $S_i$  can be mapped to the GPU and CPU,  $(m_i = 1)$ , or if it can only be mapped to the CPU  $(m_i = 0)$ . If  $m_i = 1$ , the item that enters stage  $S_i$  will check if the GPU is available, in which case it will execute on the GPU; otherwise, it will execute on the CPU. For instance, for the ViVid example of Fig. 2 we represent the tuples (row major order):  $\{1,1,1\}$ ,  $\{1,0,0\}$ ,  $\{0,1,0\}$ ,  $\{0,0,1\}$ ,  $\{1,1,0\}$ ,  $\{1,0,1\}$ ,  $\{0,1,1\}$ ,  $\{0,0,0\}$ .

Once the pipeline is configured for a static configuration, it can be run (line 15) by setting the maximum number of items that are allowed to be simultaneously in flight traversing the pipeline. Another option to run the pipeline is to use the adaptive configuration mode (line 18) presented in section IV. Under this mode, our framework dynamically finds the best configuration. In this case, the user has to select the optimization criterion (THROUGHPUT, ENERGY, THROUGHPUT\_ENERGY) and the maximum overhead allowed due to the training step required when running in the adaptive mode explained in section IV.

```

* 2.- Pipeline declaration and usage

2

3

4 int main(int argc, char* argv[]) {

int numThreads = nC+1; // number of threads = nC+1

h_pipeline::pipeline<ViVidItem> pipe(numThreads);

6

// Set CG, MG and GPU functions for each stage

8

pipe.add_stage(cg_f1, mg_f1, gpu_f1);

pipe.add_stage(cg_f2, mg_f2, gpu_f2);

9

10

pipe.add_stage(cg_f3, mg_f3, gpu_f3);

11

12

13

//Setting a static pipeline configuration: mapping '111' and MG

pipe.set_configuration({1,1,1}, h_pipeline::USE_MG);

14

15

pipe.run(numTokens); // maximum number of items in flight

16

//Dispatch of the adaptive configuration mode for the pipeline

17

//pipe.run(numTokens, ENERGY, maxoverhead);

18

19

```

Fig. 5: Pipeline declaration and usage.

# C. Pipeline stage functions

An important part of the pipeline definition is the set up of the pipeline stage functionalities. In the interface, the add\_stage() method (Fig 5, lines 9 to 11) is used to add each one of the stages while identifying the possible functions that may be called to process the items.

Fig. 6 shows an example of these stage functions definition. The programmer can provide three different versions of the same function. The pipeline will use the appropriate version of the function to map the stage to one CPU core, several CPU cores, or the GPU device. Each function receives as argument a pointer to the item to be processed. From such item we can obtain the pointers to the input/output data buffers by using the method get\_HOST\_PTR() to obtain a host pointer, or get\_CL\_BUFFER() to obtain an OpenCL buffer object usable at the GPU device. In both cases, the access type to that buffer inside the function must be indicated by the programmer (options are: BUF\_READ, BUF\_WRITE, BUF\_READWRITE).

Fig. 6 shows the definition of two functions that can be invoked on the CPU and a third one to process an item on the GPU. First, in line 5 we have the CPU function for CG granularity, that is basically a serial code to process an item on the CPU. For this granularity, parallelism is exploited at the task level since several cores may be running this function at the same time for different items. Next in line 13, we have the definition for MG granularity, were all the cores will collaborate in processing a single item. Now, data parallelism is

8

```

2 * 3.- Functions definition example

3

********/

// Example for filter 3 of ViVid

4

5 void cg_f3(ViVidItem *item) // Coarse grain CPU version

6

{

float * out, cla, his;

7

out = item->out->get_HOST_PTR(BUF_WRITE); // get buffer on host for writing

8

cla = item->cla->get_HOST_PTR(BUF_READ); // get buffer on host for reading

his = item->his->get_HOST_PTR(BUF_READ); // get buffer on host for reading

9

his = item->his->get_HOST_PTR(BUF_READ);

10

11

// do cpu things like out[XXX] = his[XXX] + cla[XXX];

}

12

13 void mg_f3(ViVidItem *item) // Medium grain CPU version

14

float * out, cla, his;

15

16

out = item->out->get_HOST_PTR(BUF_WRITE); // get buffer on host for writing

cla = item->cla->get_HOST_PTR(BUF_READ); // get buffer on host for reading

his = item->his->get_HOST_PTR(BUF_READ); // get buffer on host for reading

17

18

19

tbb::parallel_for( 0, aheight, 1, [&] (size_t i) {

20

21

// do cpu things like out[i] = his[i] + cla[i];

22

23

24

// #pragma omp parallel for

// for (size_t i=0; i<aheight; i++) {</pre>

25

26

// do cpu things like out[i] = his[i] + cla[i];

27

// }

28

}

29 void gpu_f3(ViVidItem *item) // GPU OpenCL version

30

31

cl_mem out,cla,his;

out = item->out->get_CL_BUFFER(BUF_WRITE); // get buffer on device for writing

32

cla = item->cla->get_CL_BUFFER(BUF_READ); // get buffer on device for reading

his = item->his->get_CL_BUFFER(BUF_READ); // get buffer on device for reading

33

34

35

36

// Setting kernel parameters

37

// Launching kernel

38

39

}

```

Fig. 6: Functions for pipeline stages operations (CG, MG, GPU).

exploited, and to that end in this example we rely on tbb::parallel\_for() (line 20). MG granularity can be also exploited using OpenMP as shown in commented line 24. Finally we have the GPU code defined in the gpu\_f3 function (line 29). Note also that pipeline parallelism is exploited because concurrent items traverse the stages of a pipeline at their own pace.

# D. Buffers

As shown previously in Fig. 4, thanks to our Databuffer<T> template class, the programmer does not need to manage memory buffers explicitly. The supplied buffer class hides all the data buffer management and the programmer just need to ask for the references to the buffers he wants to use, indicating whether the buffers will be read or/and written. Fig. 7 shows an example of buffer declaration and access. In line 5 a data buffer is declared. In the next line a pointer, \*frame, is declared to access the former data buffer from the CPU.

The DataBuffer class offers a way to set up the type of access to a certain OpenCL buffer, so a method to set it up must be used (line 9) and we can choose to use a Zero-Copy Buffer approach (line 10) or copy data from host CPU to device (and viceversa) when required.

On the creation of the buffer (line 9) we need to indicate the kind of access that this buffer will take from the OpenCL kernel (read or/and write). The actual allocation of the buffer (on host or device memory) will be delayed until the first use. To use the buffer the programmer will invoke the right method: get\_HOST\_PTR() to obtain a host pointer, or get\_CL\_BUFFER() to obtain a device memory object. In the example of Fig. 7 (line 14), the host pointer, frame, is initialized using get\_HOST\_PTR() with write intent. In the next line the buffer is initialized with the appropriate data.

```

2 * 4.- BUFFER usage

3 ***************

*************************

4 int main(int argc, char* argv[]){

DataBuffer<float> * global_frame; // data buffer

5

float *frame;

// pointer to access the buffer from CPU

7

//Specify access mode for OpenCL kernel: BUF_READ BUF_WRITE BUF_READWRITE

8

global_frame = new DataBuffer<float>(size, BUF_READ);

9

global_frame->set_ZCB(true); //Set Zero Copy Buffer usage

10

11

global_frame->use_Pool(true); //Use a pool of buffers

12

13

//acquire the buffer reference to write it on the CPU

14

frame = global_frame->get_HOST_PTR(BUF_WRITE);

frame[XXX] = XXX; // fill the buffer on the CPU

15

16

//Pipeline definition and usage

17

. . .

18 }

```

Fig. 7: Example of DataBuffer class usage.

#### E. Implementation details

In this section we dive into the internal details of the framework that we have implemented. First, we describe the parallel stage class and finally we elaborate on the implementation of the pipeline class.

```

2 * Parallel Stage Internal Details

4 template <class Item_T>

5 class parallel_stage : public tbb::filter{

//members

6

int runOnGPU; //1 runs on GPU, 0 runs on CPU

7

bool grain; //True is MG, False is CG

8

void (*cqFunc)(Item_T*);

9

void (*mgFunc)(Item_T*);

10

11

void (*gpuFunc) (Item_T*);

12

13

//Constructor

parallel_stage(void (*cg_f)(Item_T*), void (*mg_f)(Item_T*), void (*gpu_f)(Item_T*)){

14

cgFunc=cg_f; mgFunc=mg_f; gpuFunc=gpu_f;

15

16

17

//Methods

void setConfiguration(int mapping, bool granularity) {

18

19

runOnGPU = mapping; grain = granularity;

20

}

21

void * operator() (void * item) {

22

Item_T *it = (Item_T *) item;

23

if (runOnGPU && h_pipeline::isGPUidle()) {

24

25

gpuFunc(it);

26

}else if(grain){

27

mgFunc(it);

28

}else{

29

cgFunc(it);

30

}

31

return it;

32

}

33 };

```

Fig. 8: Internal details of parallel\_stage class.

1) Pipeline Stages: One of the key components of the pipeline<T> class is the parallel\_stage class. One object of this class is allocated for each add\_stage() invocation (see Fig. 5 lines 9 to 11). This class holds important instance variables: three of them are function pointers (see Fig. 8 lines 9-11) which point to the functions declared in Fig. 6 (they are initialized in the class constructor at line 14). The other two instance variables, runOnGPU and grain, are used to decide whether the stage should execute on CPU or GPU (at runtime) and in the former case, if the MG or CG version should be used to execute the stage on the CPU. The operator() function (line 22) is automatically invoked when an item reaches the stage.

This functor first receives a pointer to the item that needs to be processed so it can be passed down to the appropriate function. Then it is decided which function has to be called: if runOnGPU is true and the GPU is idle, the item is processed on the GPU (i.e. gpuFunc is called). Otherwise, depending on the grain, mgFunc or cgFunc will be invoked.

```

2 * pipeline class inner details

3

4 template <class Item T>

5 class pipeline : public tbb::pipeline {

//members

6

atomic<int> gpuStatus; //0 GPU is idle, 1 GPU is busy

7

8

list<parallel_stage> l_stage;

int num_stages, nthreads;

9

10

11

//Constructor

pipeline(int numthreads) {

12

//Initialize TBB scheduler and OpenCL boilerplate

13

num_stages=0; nthreads=numthreads;

14

15

16

17

//Adding Stages

void add_stage(void (*cg_f)(Item_T*), void (*mg_f)(Item_T*), void (*gpu_f)(Item_T*)){

18

parallel_stage<Item_T> * iStage(cg_f, mg_f, gpu_f);

19

20

l_stage.add(iStage, ++num_stages);

21

}

22

//Setting Configuration for all stages

23

void set_configuration(int mappings[], bool granularity){

24

25

for(int i=0; i<num_stages; i++) {</pre>

26

l_stage.get(i).setConfiguration(mapping[i], granularity);

27

}

28

}

29

30

//Overloaded pipeline.run(): static configuration mode

31

void run(int tokens) {

32

//Build the TBB pipeline and run it

33

34

//Overloaded pipeline.run(): adaptive configuration mode

35

void run(int tokens, const int criteria, float overhead) {

36

while(/*there are more items*/){

37

38

//Training Phase:

setConfiguration({1,1,1}, USE_MG); pipe.run_training(1);

39

40

setConfiguration({0,0,0}, USE_MG); pipe.run_training(1);

41

setConfiguration({0,0,0}, USE_CG);

for(int i=1; i<=(nthreads+1);i++) {</pre>

42

43

pipe.run_training(i);

44

45

computeModelAndSetBestConfiguration(criteria);

46

47

//Running Phase: It can abort if a change in throughput is detected

48

pipe.run_monitoring(tokens);

49

50

}

51

. . .

52 };

```

Fig. 9: Internal details of pipeline class.

2) Pipeline class: In this section we introduce some internal details regarding the pipeline<T> class. This class is at the top of the software stack described in Fig. 3b, so it is designed to work on top of TBB and OpenCL libraries. Fig. 9 sketches the main implementation decisions we have considered for this pipeline<T> class.

The pipeline class is the main component of the library, it is responsible to glue the set of stages and schedule the items in flight to maximize the optimization criteria. In order to make this possible the pipeline class defines a few member variables (lines 7-9). The gpuStatus variable shows the current status of the GPU at runtime: it can be (0 = Idle and 1 = Busy). This class also defines an ordered list of stages, (l\_stage), that represents the stages of the pipeline. Additionally, there are two integer variables: nthreads which is used to set the number of logical threads to be created and num\_stages which has the current count of parallel stages in the list. The class constructor (line 12) initializes the TBB library with the number of threads passed as argument. Then the constructor creates the OpenCL environment (context, command\_queues, ...) and selects the GPU as the target device.

The pipeline class defines two methods (add\_stage and set\_configuration) to configure the topology of the pipeline. As mentioned before, this class keeps a list of stages, where the Input and Output stages (first and last ones) are serial. For each one of the middle stages (parallel or stateless) the function add\_stage is called with three function pointers passed as arguments (CG, MG, GPU), so a new parallel\_stage instance is created and inserted in the list (line 18). The set\_configuration (line 24) method allows the user to set a specific pipeline configuration. This method receives two parameters: an array of zeros and ones, where the i-th element specifies whether the i-th stage can use the GPU (1) or not (0). The second parameter is an enumerated type that sets the type of CPU functor (USE\_MG for Medium Grain, MG, or USE\_CG for Coarse Grain, CG) that should be used for all stages.

In order to execute the pipeline, the run method must be invoked. Notice that it is possible to invoke two versions of the pipeline.run() method (lines 31 and 36), thus two types of modes are available: a static configuration or an adaptive configuration mode. The former (line 31) has a static behavior. This means that just one pipeline configuration is used during the whole execution of the pipeline. In this case, the user is responsible to set the particular pipeline configuration by calling the function set\_configuration (i.e. pipe.set\_configuration({1,1,1}, USE\_MG)) (see line 14 in Fig. 5). The adaptive configuration mode of the run method (line 36) takes three arguments: the maximum number of items in flight, the optimization criteria (THROUGHPUT, ENERGY, THROUGHPUT\_ENERGY) and a float number between 0 and 1 that represents the allowed overhead ratio (see section IV-B).

The adaptive configuration run method has 2 phases: the training phase and the running phase (see section IV). The training phase carries out three experiments. The first one executes one item on the GPU through all stages (line 39). The second one executes one item on the CPU with MG granularity (line 40) on all stages. Finally, the third experiment launches nthreads (from 1 to nthreads) executions on the CPU with CG granularity (line 43). More details in section IV-A. Notice that the run\_training method is used here. Then we compute our analytical model (line 45) with the time and energy collected in the previous experiments and the desired optimization criteria. This analytical model returns the best configuration that maximizes the optimization criteria passed as argument. This model is explained with deeper details in section V.

Once the desired configuration is found, the pipeline enters in the second phase (running phase). In this phase, the run\_monitoring method (line 48) always monitors the throughput and energy. Whenever a change (drop/rise) in throughput is detected, the pipeline checks the overhead parameter and the number of items processed in this phase. If the ratio between the total time taken by the previous training phase and the execution time of the current phase is less than the overhead threshold, then the current running phase is aborted and the training phase is executed again. Otherwise the algorithm continues in the running phase until the overhead ratio is less than the overhead. More details about the computation of the overhead in section IV-B.

#### IV. FRAMEWORK

Our framework is particularly suitable for streaming applications that may exhibit a variation in the streaming characteristics. In these cases, we can adjust the pipeline configuration to optimize the desired metric (throughput, or energy, or a tradeoff). Our framework is designed as a two phase engine: first, a *training phase* followed by a *running phase*. The training phase carries out two steps: i) *a measurement collection step*, where some measurements of time and energy are performed on the GPU and CPU; and ii) *an analytical evaluation step*, where our model (see next section) finds the optimal pipeline configuration using the collected measurements. Once the optimal configuration has been found, the framework enters the running phase. In order to adapt to variations in the behavior of the applications, throughput is monitored during the running phase is only performed if the associated overhead is less than a threshold value provided by the user (more details in subsection IV-B).

During the training phase, runtime items are used, so no off-line training is necessary. Also, the runs to collect the measurements are conducted only on the CPU or on the GPU (homogeneous runs). Then, using the proposed model, the framework can predict the behavior of all possible heterogeneous pipeline configurations and select the best.

We assume that the *s* parallel stages of our streaming application are  $S_1$ ,  $S_2$ , ...,  $S_s$  and that each item will be executed through all these stages. Additionally, we consider that both the Input and Output stages are serial ( $S_i$ ,  $S_o$ ), although this is not a pre-requisite in our model. Our model is based on a set of equations that allow us to estimate the throughput and energy consumption per item for all possible pipeline alternatives. Let's suppose that our system consists of nC CPU cores and 1 on-chip GPU. Then, our framework traverses the  $2^s \cdot (nC+2)$  possible pipeline configurations, and for each one computes the effective throughput,  $\lambda_e$ , and the effective energy per item,  $E_e$ . From the estimations, it selects the pipeline configuration for which the optimal is found: highest  $\lambda_e$  or lowest  $E_e$ , depending on the metric considered. We can also use any combination of these metrics to define a tradeoff metric and look for the configuration which obtains the optimal value.

# A. Measurement Collection step

As mentioned, the equations of our model use the data recorded in the measurement collection step. In this step, we carry out nC + 3 experiments to obtain all the values needed. Note that this number of experiments is usually much smaller than the  $2^s \cdot (nC+2)$  possible alternatives, that thanks to the model we do not need to experimentally assess. For time measurements we use the clock ticks hardware counter, while for the energy measurements, we use the energy counters available on the Ivy Bridge and the Haswell architectures [14], [15]. These counters measure three domains: P, C and G. P or Package means the consumption of the whole chip, including CPU, GPU, memory hierarchy, etc. C is CPU domain and G is the GPU domain. In our model we consider C, G and U = P - C - G. Therefore, this last component represents the Uncore energy consumption. For other architectures, energy information can be estimated by either relying on performance counters that can be read by using a library, such as PAPI [16], or by using a power sensor, like the INA231 power monitor integrated with the Exynos 5 on the Odroid XU3 platform [17]. Current trends point out that energy counters will be more widely available in the near future. Anyway, even if energy information is not accesible, our framework is still useful to minimize execution times.

The experiments and measurements we collect are always from homogeneous runs (only GPU or CPU execution). These experiments are:

- CG experiments: we perform 1 experiment in which all stages are executed by one thread in one CPU core. We collect time and energy per stage (see  $T_k^{CG}$  and  $(E_{C_k}^{CG}, E_{G_k}^{CG}, E_{U_k}^{CG})$ , k = 1 : s, in Table I). For energy measurements we collect three components (C, G, U) as explained before. Next, we carry out nC additional experiments in the CPU multicore: on each one, n threads (with n changing from 2 to nC+1) process n items (each thread processes one item) throughout all the pipeline stages, i.e. homogeneous CG executions. We collect the total time and energy per item (see  $T^{CG}(n)$  and  $(E_C^{CG}(n), E_G^{CG}(n), E_U^{CG})$ , n = 2 : nC+1, Table I). Note that the case for one thread was already considered in the first experiment described above. Actually,  $T^{CG}(1) = \sum_{1}^{s} T_k^{CG}$  and  $E_*^{CG}(1) = \sum_{1}^{s} E_{*_k}^{CG}$ , where \* takes the value C, G and U. With these measurements we implicitly incorporate to the model the impact that n threads processing n items have in the memory traffic as well as the scalability behavior in the CPU. To carry out these nC+1 experiments,  $(nC+2) \cdot (nC+1)/2$  items of the stream are processed.

- MG experiments: we conduct 2 additional experiments in which all stages are executed first by one thread in the GPU, and next by nC threads in the CPU multicore, i.e. homogeneous MG execution, where nC is the number of CPU cores. We collect time and energy per stage (see  $T_k^G$  and  $(E_{C_k}^G, E_{G_k}^G, E_{U_k}^G)$ ), k = 1: s, for the GPU and  $T_k^{MG}$  and  $(E_{C_k}^{MG}, E_{G_k}^{MG}, E_{U_k}^{MG})$ , k = 1: s, for MG on the CPU, in Table II). Two additional items of the stream are processed to carry out these two MG experiments.

TABLE I: Measured time per item, T, and energy per item, E, for CG. Also time to collect them. Note that in practice,  $T^{CG}(1) = \sum_{1}^{s} T_{k}^{CG}$ ,  $E_{*}^{CG}(1) = \sum_{1}^{s} E_{*_{k}}^{CG}$ , where \* takes the value C, G and U, and  $t^{CG}(1) = t^{CG}$ , so no additional experiment need to be conducted for 1 thread.

| Parameter                                                                                                                         | Device | time col.                       | Description                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------------|------------------------------------------------------------------------------------------|

| $T_1^{CG}, \ldots, T_s^{CG}$                                                                                                      | CPU    | $_{t}CG$                        | time per item (and stage) on the CG exec. (1 thread)                                     |

| $ \begin{pmatrix} E_{C_1}^{CG}, E_{G_1}^{CG}, E_{U_1}^{CG} \\ \cdots \\ (E_{C_s}^{CG}, E_{G_s}^{CG}, E_{U_s}^{CG} \end{pmatrix} $ | CPU    | U                               | (C,G,U) components of the energy per item (and stage) on the CG exec. (1 thread)         |

| $T^{CG}(1), \dots T^{CG}(n_m)$                                                                                                    | CPU    | $t^{CG}(1), \ldots t^{CG}(n_m)$ | total time per item on the CG exec. (1, 2 $n_m = nC + 1$ threads)                        |

| $ \frac{\left(E_C^{CG}(1), E_G^{CG}(1), E_U^{CG}(1)\right)}{\left(E_C^{CG}(n_m), E_G^{CG}(n_m), E_U^{CG}(n_m)\right)} $           | CPU    |                                 | (C,G,U) comp. of the total energy per item on the CG exec. (1, 2 $n_m = nC + 1$ threads) |

Notice that the model can also be used when hyperthreading is enabled. To consider the use of hyperthreading, the collecting measurement step needs to run nC \* 2 + 3 (instead of nC + 3) experiments.

TABLE II: Measured time per item, T, and energy per item, E, and per stage for GPU and for MG. Also time to collect them.

| Parameter                                                                                                                                  | Device | time col. | Description                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------|------------------------------------------------------------------------|

| $T_1^G, \ldots, T_s^G$                                                                                                                     | GPU    | +G        | time per item (and stage) on the GPU exec. (1 thread)                  |

| $\begin{pmatrix} E_{C_1}^G, E_{G_1}^G, E_{U_1}^G \\ \cdots \\ \begin{pmatrix} E_{C_s}^G, E_{G_s}^G, E_{U_s}^G \end{pmatrix} \end{pmatrix}$ | GPU    | L         | (C,G,U) components of the energy per item (and stage) on the GPU exec. |

| $T_1^{MG}, \ldots, T_s^{MG}$                                                                                                               | CPU    | +MG       | time per item (and stage) on the MG exec. (nC threads)                 |

| $\begin{pmatrix} E_{C_1}^{MG}, E_{G_1}^{MG}, E_{U_1}^{MG} \\ \cdots \\ (E_{C_s}^{MG}, E_{G_s}^{MG}, E_{U_s}^{MG} \end{pmatrix}$            | CPU    | L         | (C,G,U) components of the energy per item (and stage) on the MG exec.  |

# B. Controlling the overhead of the measurement collection step

The cost of the training phase is mainly due to the measurement collection step, where items are processed inefficiently due to the homogeneous runs (only one device is used at a time) carried out during this step. After the measurement collection step and the subsequent model instantiation, we can control the period of time at which a new training can be performed to guarantee that the overhead due to the training is bounded. Let's suppose that  $\lambda_c$  is the throughput to process items in the current configuration (after performing the last training) and that  $N_s = (nC+2) \cdot (nC+1)/2 + 2$  is the number of items processed during the measurement collection step (see Tables I and II). We define  $\Delta t$  as the overhead or time increment incurred during that last training. It is computed as the time needed to carry out the collection step minus the time the  $N_s$  items would have taken at the current  $\lambda_c$  throughput:

$$\Delta t = \left(t^{CG} + \left(\sum_{n=2}^{nC+1} t^{CG}(n)\right) + t^{MG} + t^G\right) - N_s/\lambda_c \tag{1}$$

The *overhead* that the last training has supposed with respect to the current throughput can be computed as,

$$ov = \frac{\Delta t}{t+\Delta t}$$

We can keep this overhead below a threshold value,  $ov_{thl}$ , if  $\Delta t/(\Delta t + t) < ov_{thl}$ , or in other words:

$$t > \frac{(1 - ov_{thl})}{ov_{thl}} \cdot \Delta t \tag{2}$$

This expression gives us a lower bound for controlling the time for entering in a new training phase, t, with a maximum allowed overhead. For example, for the ViVid application on the Ivy Bridge chip presented in section VI, 5% of overhead is paid when the training takes place every 3.7 sec. for low resolution input video. However, in general, the training phase leads to pipeline configuration changes that deliver a better throughput which result in that the training overhead is amortized after processing a few items with the new recommended pipeline configuration, as we discuss in section VI.

# V. ANALYTICAL MODEL: FINDING THE OPTIMAL

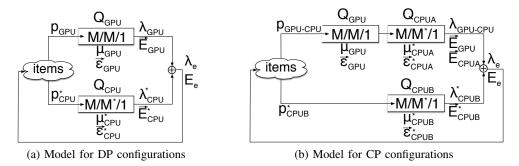

We model the heterogeneous pipeline configurations as a closed network of logical queues where items arrive following a Poisson process [18]. This is pertinent in the context of streaming applications where item arrivals can be considered independent and inter-arrival time can be viewed as following an exponential distribution [19]. In these closed systems, items can be viewed as circulating continuously and never leaving the network of queues, because a new item can not enter until a previous one leaves. Fig. 10 shows our models for the Decoupled and Coupled configurations, where we can see that an item can follow one of two alternative paths before entering again in the system. In our models, we can find one or more queues on each path. In particular, any sequence of consecutive stages mapped to one device (the GPU or the CPU) is represented as a M/M/1 queue. This stands for a logical queue where a single server serves items that arrive according to

a Poisson process and have exponentially distributed service times. Although there can be several concurrent threads on a device processing the sequence of stages represented by the queue, we have found that assuming one logical server on each queue still provides accuracy while keeping the equations of the model simple. In a closed network of queues, the following expressions define the *flow balance conditions* [20] at equilibrium,

$$\lambda_e = \sum_{path_j} \lambda_j \tag{3}$$

$$\sum_{path_j} p_j = 1 \tag{4}$$

$$p_j \cdot \lambda_e = \lambda_j \tag{5}$$

These equations allow us to relate the relative throughput of each path in a configuration with the effective throughput in that configuration. A path  $path_j$  refers to one of the two possible paths defined in section II for each configuration: for DP configurations, it is either the GPU path or the CPU path (note the subindices for each path (GPU, CPU) in the model in Fig. 10a); For CP configurations, it is either the GPU-CPU path or the CPU path (note the subindices for each path (GPU-CPU, CPUB) in the model in Fig. 10b). In particular, equation 3 establishes that given the relative throughputs of the paths in the system,  $\lambda_j$ , then the effective throughput,  $\lambda_e$ , may be obtained as a sum (i.e. combining independent Poisson processes leads to a Poisson process). Equation 4 states that splitting a Poisson process probabilistically leads to Poisson processes, being  $p_j$  the probability of taking  $path_j$ . Equation 5 states that, in a M/M/1 queue at equilibrium, the average flow rate leaving the queue will also be the same as the average flow rate entering the queue.

We define two parameters for each queue  $Q_i$ : the *service rate*,  $\mu_i$ , or average rate at which an item is processed, and the *energy rate*,  $\vec{\epsilon}_i$ , or average energy consumed by an item in the corresponding device (GPU or CPU) where the queue works. This parameter represents a vector with three components, one for each energy domain:  $(\varepsilon_{i_C}, \varepsilon_{i_G}, \varepsilon_{i_U})$ . They can be seen as the components of the average energy consumed by an item on a device due to the stages represented by the queue  $Q_i$ , when the device is the only one working in the system (homogeneous execution).

In any case, as the network is in equilibrium, each individual queue must be in equilibrium. This means that the utilization of the queue's server,  $\rho_i$ , is less than 100%, that is, the ratio between the relative throughput of the corresponding path,  $\lambda_j$ , and the queue's service rate,  $\mu_i$ , is at most 1 [18],

$$\rho_i = \frac{\lambda_j}{\mu_i} \le 1 \tag{6}$$

Fig. 10: Closed network of queues.

Regarding the energy, as each individual queue  $Q_i$  is in equilibrium, we assume that the energy utilization on the corresponding device,  $\rho_i^{\vec{E}}$ , is proportional to the probability of items serviced on the corresponding queue,  $p_j$ , or in other words,

$$\rho_i^{\vec{E}} = p_j \le 1, \quad \vec{E}_i = \rho_i^{\vec{E}} \cdot \vec{\varepsilon}_i \tag{7}$$

This expression allows us to estimate the *relative energy per item* consumed by queue  $Q_i$  on the corresponding device (GPU or CPU),  $\vec{E}_i$ . This parameter is also a vector that consists of three components:  $(E_{i_C}, E_{i_G}, E_{i_U})$ . In the case there were several logical queues mapped on a device, from  $Q_1$  to  $Q_d$ , then the relative energy per item consumed by the queues in the device is the sum of the relative energy per item for all the queues working in the device:  $\sum_{i=1}^{d} \vec{E}_i = \left(\sum_{i=1}^{d} E_{i_C}, \sum_{i=1}^{d} E_{i_G}, \sum_{i=1}^{d} E_{i_U}\right)$ . These components can be seen as the components of the energy consumed by the items that a device processes when the device is the only one working in the system (homogeneous execution).

However, the effective energy consumed by the GPU and CPU when both devices are working in the system (heterogeneous execution), is not the sum of the relative energies of the queues on each device. Let's define the *effective energy per item* consumed in the system,  $E_e$ , as,

$$E_e = \min\left(\frac{TDP}{\lambda_e}, E_{e_C} + E_{e_G} + E_{e_U}\right) \tag{8}$$

where TDP is the power budget of the chip,  $\lambda_e$  the effective throughput, and  $E_{e_c} + E_{e_d} + E_{e_u}$  the effective energy consumed when the TDP is not reached. For the heterogeneous chips studied, we have found that in case the TDP is not reached, then each component of the effective energy is given by the dominant component of the relative energy computed for each device. This is what we call the *energy balance condition*. Let's suppose that the relative energy per item for all the queues in the GPU device is given by  $\vec{E}_{GPU} =$  $(E_{GPU_{C}}, E_{GPU_{G}}, E_{GPU_{U}})$ , and the relative energy per item for all the queues in the CPU device is given by  $\vec{E}_{CPU} = (E_{CPU_G}, E_{CPU_G}, E_{CPU_U})$ . The rationale for the energy balance condition is that the C-component of the effective energy is typically dominated by the C-component of the relative energy of the CPU device,  $E_{CPU_{C}}$ , while the C-component of the GPU device,  $E_{GPU_{C}}$  is just a "residual" or standby consumption when the CPU is idle. Remember that this C-component of the relative energy of the GPU device is obtained with homogeneous runs (runs on the GPU where the CPU is idle) during the measurement collection step. On an heterogeneous run, however, the CPU is not idle, and so the standby consumption measured during the homogeneous run is already included in the C-component of the relative energy of the CPU,  $E_{CPU_{c}}$ , and does not need to be included again. A similar argument can be made for the G-component of the effective energy. With respect to the U-component, we have observed that the effective energy consumed is determined by the device (CPU or GPU) that processes a higher load.

Next, Sections V-A and V-B explain how we model Decoupled and Coupled configurations, respectively, and how we incorporate the granularity to the models.

# A. Model for Decoupled configurations

These configurations are shown in Figs. 1a and 1c (DP-CG and DP-MG, respectively). Fig. 10a depicts our model for them. As explained in section II, in these configurations there is a GPU path in which a thread processes an item through all stages in the GPU, and also there is a CPU path in which n concurrent threads process other item/s through all the stages in the CPU device.

The GPU device is modeled with  $Q_{GPU}$  which is the M/M/1 queue that services all the stages for the items that go through the GPU path. This queue is characterized with two parameters:  $\mu_{GPU}$ , the service rate of the GPU server, and  $\overrightarrow{e}_{GPU}$ , the energy rate consumed by the queue in the GPU device. These parameters are computed from the time and energy measurements taken in the collection step, as we show in Table III. For both parameters we consider the time and the energy per item of all the stages  $S_k$  that are mapped to the GPU (k from 1 to s, see Table II).

The CPU device is modeled with  $Q_{CPU}$  which is the M/M\*/1 queue that services all the stages for the items that go through the CPU path. The \* stands for the different instantiations of the queue, depending on the granularity exploited. For the CG granularity, the queue is characterized with two parameters:  $\mu_{CPU}^{CG}(n)$ , the service rate of the CPU server under CG granularity, and  $\vec{\epsilon}_{CPU}^{CG}(n)$ , the energy rate consumed by the queue in the CPU device under CG granularity. Note that under the CG granularity the CPU device can run from 0 to nC concurrent threads. The n = 0 case represents in fact the GPU homogeneous execution, while the n = nC represents the maximum number of threads in the CPU path. Therefore, for the CG granularity, both the service rate and the energy rate are computed for each possible number of threads. Table III shows

how these parameters are computed, where we see that time and energy are taken from the measurements in Table I. Regarding the MG granularity, the queue is defined by  $\mu_{CPU}^{MG}$  and  $\vec{\epsilon}_{CPU}^{MG}$ . In Table III we show these parameters, where we notice that time and energy are taken from the measurements in Table II.

| Parameter                                    | Device / Gr. | Value                                                                                                | Description                                                                        |  |  |  |

|----------------------------------------------|--------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|

| $\mu_{GPU}$                                  | GPU          | $\frac{1}{\sum_{k=1}^{s} T_k^G}$                                                                     | service rate for the stages mapped to the GPU                                      |  |  |  |

| $\overrightarrow{\varepsilon}_{GPU}$         | GPU          | $\left(\sum_{k=1}^{s} E_{C_k}^G, \sum_{k=1}^{s} E_{G_k}^G, \sum_{k=1}^{s} E_{U_k}^G\right)$          | energy rate consumed by the stages mapped to the GPU                               |  |  |  |

| $\lambda_{GPU}$                              | GPU          | $\mu_{GPU}$                                                                                          | relative throughput of the GPU path                                                |  |  |  |

| $\overrightarrow{E}_{GPU}$                   | GPU          | $p_{GPU} \cdot \overrightarrow{\varepsilon}_{GPU}$                                                   | relative energy per item consumed by $Q_{GPU}$                                     |  |  |  |

| $\mu_{CPU}^{CG}(n)$                          | CPU / CG     | $\frac{1}{T^{CG}(n)}, \ n = 0: nC$                                                                   | service rate for the stages mapped to the CPU under CG granularity and $n$ threads |  |  |  |

| $\overrightarrow{\varepsilon}_{CPU}^{CG}(n)$ | CPU / CG     | $(E_C^{CG}(n), E_G^{CG}(n), E_U^{CG}(n)), n = 0 : nC$                                                | energy rate consumed by the stages mapped to the CPU under CG and $n$ threads      |  |  |  |

| $\mu^{MG}_{CPU}$                             | CPU / MG     | $rac{1}{\sum\limits_{k=1}^{s}T_{k}^{MG}}$                                                           | service rate for the stages mapped to the CPU under MG granularity                 |  |  |  |

| $\overrightarrow{\varepsilon}_{CPU}^{MG}$    | CPU / MG     | $\left(\sum_{k=1}^{s} E_{C_k}^{MG}, \sum_{k=1}^{s} E_{G_k}^{MG}, \sum_{k=1}^{s} E_{U_k}^{MG}\right)$ | energy rate consumed by the stages mapped to the CPU under MG granularity          |  |  |  |

| $\lambda_{CPU}^*$                            | CPU / *      | $\mu^*_{CPU}$                                                                                        | relative throughput of the CPU path                                                |  |  |  |

| $\vec{E}_{CPU}^*$                            | CPU / *      | $p_{CPU}^* \cdot \overrightarrow{\varepsilon}_{CPU}^*$                                               | relative energy per item consumed by $Q_{CPU}$                                     |  |  |  |

| $\lambda_e$                                  | GPU + CPU    | $\lambda_{GPU} + \lambda_{CPU}^*$                                                                    | effective throughput of the system                                                 |  |  |  |

| $E_e$                                        | GPU + CPU    | $\min\left(\frac{TDP}{\lambda_e}, E_{e_C} + E_{e_G} + E_{e_U}\right)$                                | effective energy per item consumed in the system. See eq. 9                        |  |  |  |

TABLE III: Parameters of the DP-\* configurations. \* stands for CG or MG. s is the number of stages.

Since our queues are in equilibrium, and we assume maximum utilization of the servers on each queue, by applying equation 6 we get  $\rho_{GPU} = 1$  and  $\rho_{CPU}^* = 1$ . From this assumption, we find that the relative throughput for each path is given by the corresponding queue's service rate, that is,  $\lambda_{GPU} = \mu_{GPU}$  and  $\lambda_{CPU}^* = \mu_{CPU}^*$ . Also, the flow balance conditions at equilibrium (equations 3-5) allow us to compute the effective throughput of the system,  $\lambda_e = \lambda_{GPU} + \lambda_{CPU}^*$ , and the probability that an item goes through the GPU path,  $p_{GPU} = \lambda_{GPU}/\lambda_e$ , or the probability that it goes through the CPU path,  $p_{CPU}^* = \lambda_{CPU}^*/\lambda_e$ .

On the other hand, by applying equation 7 we get that the energy utilization of each queue on the corresponding device is proportional to the probability of items serviced on the queue, or in other words,  $\rho_{GPU}^{\vec{E}} = p_{GPU}$  and  $\rho_{CPU}^{\vec{E}^*} = p_{CPU}^*$ . This assumption allows us to estimate the relative energy per item consumed by  $Q_{GPU}$  in the GPU device,  $\vec{E}_{GPU} = p_{GPU} \cdot \vec{\epsilon}_{GPU}$  and by  $Q_{CPU}$  in the CPU device,  $\vec{E}_{CPU} = p_{CPU}^* \cdot \vec{\epsilon}_{CPU}^*$  (for CG or MG granularities), respectively.

The effective energy per item consumed in the system,  $E_e$ , can be computed as the minimum of  $TDP/\lambda_e$ and the sum of three components, as defined in equation 8. If the TDP is not reached, then each component can be computed by the energy balance condition that establishes that each component of the effective energy is given by the dominant component of the relative energy computed for each device. In particular, this condition in the DP-\* configurations means,

$$(E_{e_C}, E_{e_G}, E_{e_U}) = max\left(\vec{E}_{GPU}, \vec{E}_{CPU}^*\right) = \\ = \left(max(E_{GPU_C}, E_{CPU_C}^*), max(E_{GPU_G}, E_{CPU_G}^*), max(E_{GPU_U}, E_{CPU_U}^*)\right)$$

(9)

#### B. Model for Coupled configurations

These configurations are shown in Figs. 1b and 1d (CP-CG and CP-MG, respectively). Fig. 10b depicts our model for them. In these configurations there is a GPU-CPU path in which a thread processes a item through some stages in the GPU and other stages in a CPU core, and there can also be a CPU path in which other concurrent threads process items through all the stages in the remaining CPU cores. To model the service

provided by a sequence of stages mapped to each device on each path, we use a logical queue. Thus, in the GPU-CPU path we can find at least a  $Q_{GPU}$  which is the M/M/1 queue that represents the sequence of consecutive stages that service an item in the GPU device, and at least a  $Q_{CPUA}$  which is a M/M\*/1 queue that represents the rest of stages that service the item in the CPU device (\* stands for the granularity studied). For simplicity, in the figure we have represented the case in which the item is first processed by some consecutive stages in the GPU, and later by the rest of stages in the CPU. In case of a mapping where the item is first processed by consecutive stages mapped to the CPU, then to the GPU, then to the CPU, and so on, the model would include more logical queues in the GPU-CPU path: first a  $Q_{CPUA}$ , followed by a  $Q_{GPU}$ , then another  $Q_{CPUA}$ , and so on.

Each  $Q_{GPU}$  queue is characterized with two parameters:  $\mu_{GPU}$ , the service rate due to the consecutive stages mapped to the GPU server, and  $\vec{\varepsilon}_{GPU}$ , the energy rate consumed by those stages in the GPU device. These parameters are computed as we show in Table IV. For both parameters we just consider the time and the energy per item of the corresponding consecutive stages  $S_k$  that are mapped to the GPU ( $S_k \in Q_{GPU}$ ). Also, each  $Q_{CPUA}$  queue is characterized with two parameters, depending on the granularity. For the CG granularity, the parameters are:  $\mu_{CPUA}^{CG}$ , the service rate due to the consecutive stages mapped to the CPU under CG granularity, and  $\vec{\varepsilon}_{CPUA}^{CG}$ , the energy rate consumed by those stages in the CPU device under CG granularity. Table IV shows how these parameters are computed, where time and energy come from measurements in Table I. Regarding the MG granularity, the  $Q_{CPUA}$  queue is defined by  $\mu_{CPUA}^{MG}$  and  $\vec{\varepsilon}_{CPUA}^{MG}$ . In Table IV we show these parameters, where we notice that time and energy are taken from measurements in Table II.

On the other hand, the stages mapped to the CPU in the CPU path, are modeled with  $Q_{CPUB}$  which is a M/M\*/1 queue. Again, \* stands for the different instantiations of the queue, depending on the granularity. For the CG granularity, the queue is characterized with:  $\mu_{CPUB}^{CG}(n)$ , the service rate of the CPU under CG granularity, and  $\overline{c}_{CPUB}^{CG}(n)$ , the energy rate consumed by the server in the CPU device under CG granularity. With CG, the CPU can run from 0 to nC concurrent threads, in addition to the coupled GPU-CPU thread that serves the GPU-CPU path. Therefore, for CG, the service rate is computed taking into account this additional coupled thread and we model it assuming that the coupled thread is interfering with the threads that are working concurrently on the CPU. We model this interference by subtracting to the service rate of n + 1 concurrent threads running in the CPU (because the CPU consists of  $Q_{CPUA}$  and  $Q_{CPUB}$ ), a virtual service rate of 1 thread that is executing in the GPU-CPU path ( $Q_{CPUA}$ , the coupled thread). The energy rate is computed for the n concurrent threads working on the queue. In any case, for CG, both the service rate and the energy rate are computed for each number of threads. Table IV shows how these parameters are computed, where time and energy come from measurements in Table I. Regarding the MG granularity, the queue is defined by  $\mu_{CPUB}^{MG}$  and  $\overline{c}_{CPUB}^{MG}$ . Under this granularity, all the CPU threads will be serving the  $Q_{CPUA}$ . Therefore, we assume that  $Q_{CPUB}$  will have a very low probability of serving new items, and so,  $\mu_{CPUB}^{MG} = 0$  and  $\overline{c}_{CPUB}^{MG} = 0$ .

In this configuration, we assume optimistic utilization of servers on each queue. By applying equation 6 we get  $\rho_{GPU} \leq 1$ ,  $\rho_{CPUA}^* \leq 1$  and  $\rho_{CPUB}^* \leq 1$ . From these expressions we find that a solution for the relative throughput for each path is given by,  $\lambda_{GPU-CPU} = min(\mu_{GPU}, \mu_{CPUA}^*)$  and  $\lambda_{CPUB}^* = \mu_{CPUB}^*$ . In general, if there were more logical queues in the GPU-CPU path, then a solution for  $\lambda_{GPU-CPU}$  could be the minimum of the corresponding service rates in the path. Again, the flow balance conditions at equilibrium (equations 3-5) lead to computing the effective throughput of the system as  $\lambda_e = \lambda_{GPU-CPU} + \lambda_{CPUB}^*$ , and the probability that an item goes through the GPU-CPU path as  $p_{GPU-CPU} = \lambda_{GPU-CPU}/\lambda_e$ , or through the CPU path as  $p_{CPUB}^* = \lambda_{CPUB}^*/\lambda_e$ .

Similar to the DP-\* configurations, we assume that the energy utilization of each queue on each device is proportional to the probability of items serviced on the corresponding queue, as defined in equation 7. This means  $\rho_{GPU}^{\vec{E}} = p_{GPU-CPU}$ ,  $\rho_{CPUA}^{\vec{E}*} = p_{GPU-CPU}$  and  $\rho_{CPUB}^{\vec{E}*} = p_{CPUB}^*$ . These expressions allow us to estimate the relative energy per item consumed on the GPU device,  $\vec{E}_{GPU} = p_{GPU-CPU} \cdot \vec{\epsilon}_{GPU}$  and on the CPU device,  $\vec{E}_{CPUA}^* + \vec{E}_{CPUB}^* = p_{GPU-CPU} \cdot \vec{\epsilon}_{CPUA}^* + p_{CPUB}^* \cdot \vec{\epsilon}_{CPUB}^*$  (for CG or MG granularities), respectively. As we see, in the CP-\* configurations we estimate the relative energy per item consumed in the CPU from the activity in  $Q_{CPUA}$  and in  $Q_{CPUB}$ . In general, if there were more logical queues in the GPU-CPU path, then all the resultant  $\vec{E}_{GPU}$  for the different  $Q_{GPU}$  should be added to estimate the relative

| Parameter                                     | Device / Gr. | Value                                                                                                                           | Description                                                                                |  |  |  |  |

|-----------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|--|--|

| $\mu_{GPU}$                                   | GPU          | $\frac{1}{\sum\limits_{S_k \in Q_{GPU}} T_k^G}$                                                                                 | service rate of stages mapped to $Q_{GPU}$ in the GPU-<br>CPU path                         |  |  |  |  |

| $\overrightarrow{\varepsilon}_{GPU}$          | GPU          | $\left(\sum_{S_k \in Q_{GPU}} E_{C_k}^G, \sum_{S_k \in Q_{GPU}} E_{G_k}^G, \sum_{S_k \in Q_{GPU}} E_{U_k}^G\right)$             | energy rate consumed by stages mapped to $Q_{GPU}$ in the GPU-CPU path                     |  |  |  |  |

| $\mu^{CG}_{CPUA}$                             | CPU / CG     | $\frac{1}{\sum\limits_{k \in Q_{CPUA}} T_{k}^{CG}}$                                                                             | service rate of stages mapped to $Q_{CPUA}$ in the GPU-<br>CPU path under CG granularity   |  |  |  |  |

| $\overrightarrow{\varepsilon}_{CPUA}^{CG}$    | CPU / CG     | $\left(\sum_{S_k \in Q_{CPUA}} E_{C_k}^{CG}, \sum_{S_k \in Q_{CPUA}} E_{G_k}^{CG}, \sum_{S_k \in Q_{CPUA}} E_{U_k}^{CG}\right)$ | energy rate consumed by stages mapped to $Q_{CPUA}$ in the GPU-CPU path under CG           |  |  |  |  |

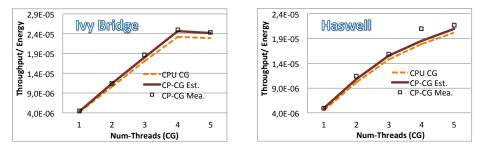

| $\mu^{MG}_{CPUA}$                             | CPU / MG     | $\frac{\frac{1}{\sum\limits_{k \in Q_{CPUA}} T_{k}^{MG}}}{S_{k} \in Q_{CPUA}}$                                                  | service rate of stages mapped to $Q_{CPUA}$ in the GPU-<br>CPU path under MG granularity   |  |  |  |  |