Introducción básica

Este vídeo presenta una introducción muy básica al uso de Logisim para crear un circuito muy simple.

Diseño e implementación de un

procesdor simple de 16 bits

Introducción

En esta página vamos a presentar paso a paso el diseño, implementación y simulación de un procesador muy simple con la herramienta de diseño y simulación lógica Logisim. Todo el proceso se presenta en unos cuantos documentos PDF con la especificación de las instrucciones y los elementos hardware básico, así como una serie de vídeos donde se presenta tanto el diseño paso a paso del procesador como su simulación.

Comenzamos con el documento de especificación de las instrucciones que va a sorportar el procesador así como los elementos hardware de los que se parte para el diseño del procesador. Esta documentación es fundamental, ya que marcará el desarrollo del procesador mostrado en los vídeos.

En este enlace puedes bajarte un proyecto base de Logisim con los elementos hardware básicos del procesador simple ya implementados (ALU, banco de registros, memoria de instrucción y memoria de datos)

En este primer vídeo se muestra el diseño del hardware necesario para la búsqueda secuencial de las instrucciones de nuestro procesador de 16 bits, utilizando la memoria de instrucción proporcionada.

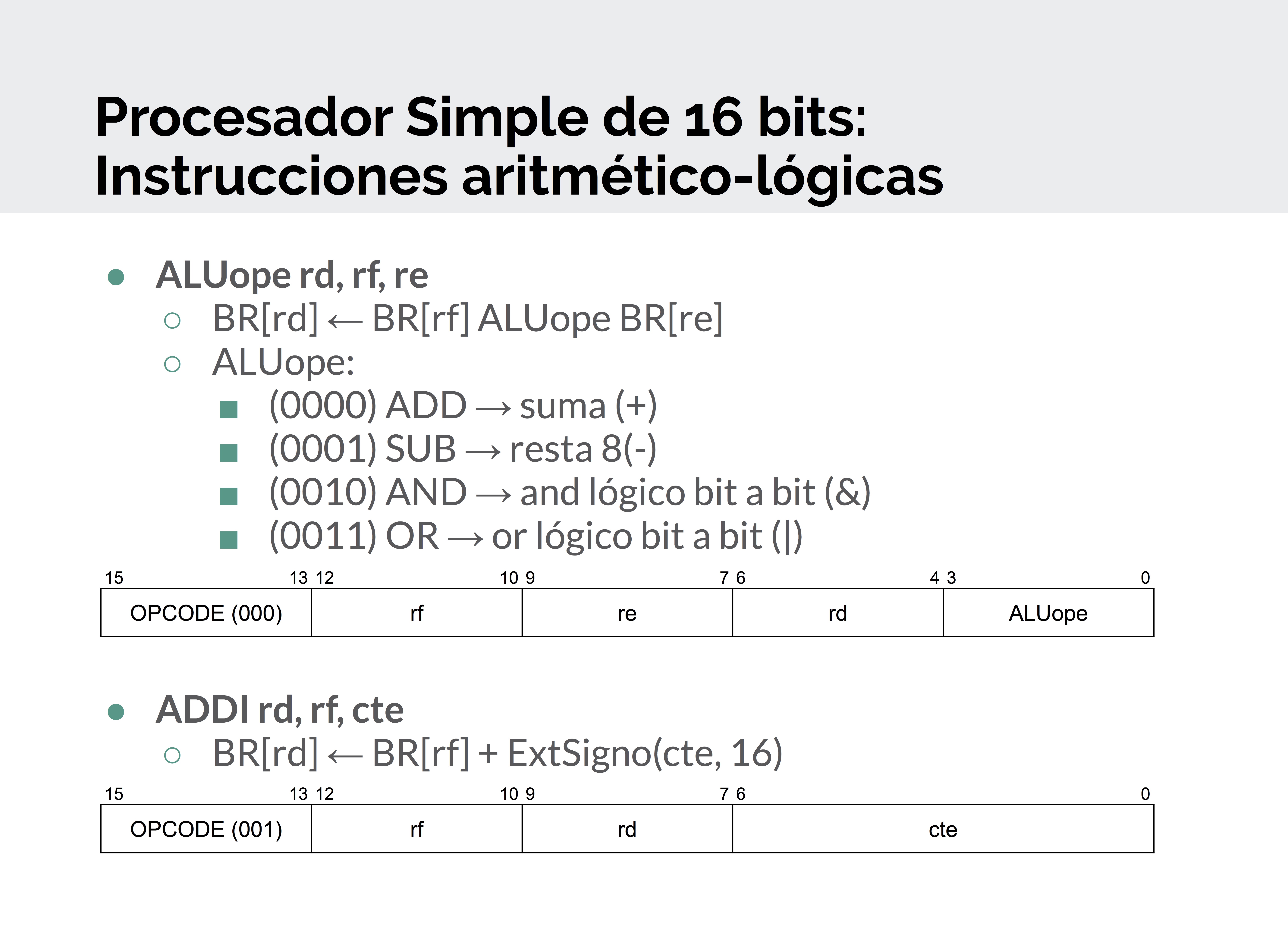

En este video se muestra la implementación de la primera instrucción del procesador, todas las operaciones ALU con fuente y destion en registros. Es especialmente interesante esta instrucción ya que, al ser la primera, se presta especial atención a la decodificación de la instrucción y a la extracción de los distintos campos de la instrucción y su uso en los diversos componentes del datapath.

Además de la memoria de instrucción utilizada ya en el video anterior, en este se utiliza el banco de registros y la ALU.

En este video se muestra el diseño e implementación de la instrucción ADDI, una suma de un registro más un inmediato. En esta segunda instrucción a parte de presentar el camino de datos necesario para su implementación, presentamos una idea fundamental de todo el diseño, como es el hecho de ir añadiendo caminos nuevos al datapath manteniendo los ya existentes para las instrucciones anteriores.

Para su implementación se utilizar un extensor de signo para pasar una constante entera representada en complemento a 2, de 7 a 16 bits, sin modificar su valor.

En estos vídeos se presenta la implementación de las dos instrucciones de nuestro procesador simple que acceden a memoria de datos: las instrucciones de carga (load, LDR) y almacenamiento (store, STR).

Este video presenta la implementación de la instrucción LDR, que leerá un dato de la memoria de datos de la posición indicada por un registro y lo almacenará en otro registro.

Para su implementación se utiliza por primera vez en el diseño la memoria de datos.

Por otro lado, este video presenta la implementación de la instrucción STR, que leerá un dato un registro y lo almacenará en la posición de memoria de datos que le especifique otro registro.

En estos vídeos se presenta la implementación de las instrucciones de salto, tanto incondicional como condicional. En concreto se implementa un salto incondicional (B) y dos condicionales, si igual (BEQ) y si menor (BLT).

Este video presenta la implementación de la instrucción B, que dado un desplazamiento de 13 bits, la siguiente instrucción a ejecutar será la almacenada en la posición de memoria calculada sumándole a PC dicho desplazamiento.

En este vídeo se presenta la primera de las dos instrucicones de salto condicional, instrucción que rompe la secuencialidad del programa saltando a la dirección calculada sumándole a PC un desplazamiento, pero solo si se cumple la condición de que el contenido de los dos registros dados es el mismo.

Por último, en este vídeo se presenta la última de las instrucciones y de los saltos, esta vez un salto si menor, instrucción similar a la anterior pero condicionada a que el primer registro dado sea menor que el segundo.

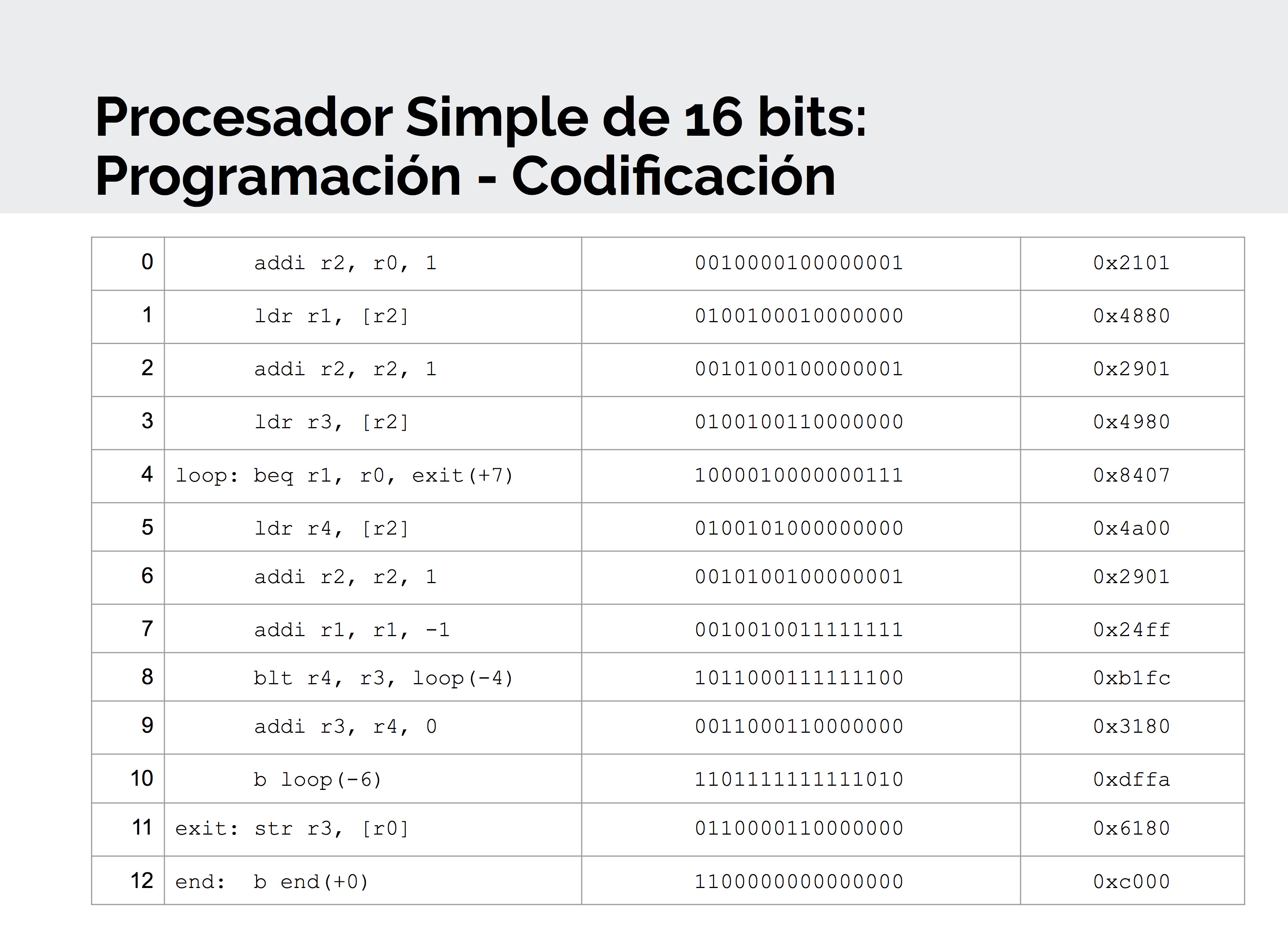

En este documento se presenta un problema de programación, su implementación en ensamblador de nuestro procesador simple, así como su codificación (binaria y hexadecimal) para poder ser escrita en el fichero asociado a la memoria de instrucciones para su posterior simulación (para ver el procesador implementado en funcionamiento ejecutando un código "real").

En este último vídeo mostramos como simular paso a paso el programa codificado anteriormente en nuestro procesador simple implementado en Logisim, y como corregir los errores que detectemos durante la simulación.

En este enlace puedes bajarte el procesador completo para simularlo tu mismo.

A continuación presentamos una serie de vídeos sobre aspectos de uso de Logisim que pueden serle de utilidad a usuarioes novéles en el uso de esta herramienta

Este vídeo presenta una introducción muy básica al uso de Logisim para crear un circuito muy simple.

Forma de crear un subcircuito para poder ser usado como si de un elemento de biblioteca se tratara en nuestro diseño.

Uso del elemento separador para la separación de la información agrupada en un bus.

Uso de los registros.

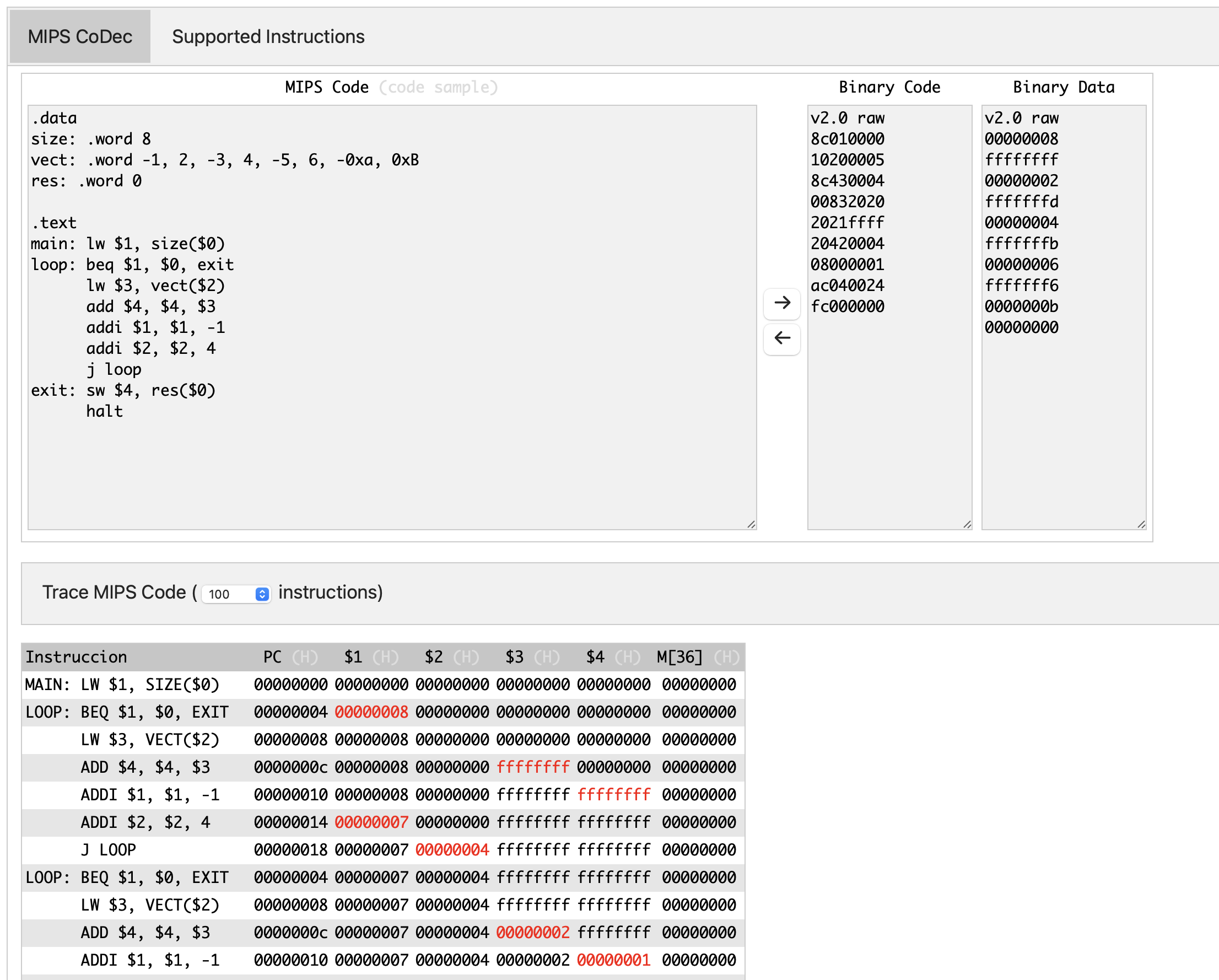

A continuación presentamos unos vídeos de apoyo para el desarrollo de un MIPS reducido (R-MIPS) que se desarrolla como práctica académica en la asignatura de Tecnología de Computadores de los grados de Informática de la Universidad de Málaga.

En este video explico el funcionamiento básico de los elementos hardware que se dan de base para el diseño del procesador MIPS reducido (R-MIPS): memoria de instrucción, memoria de datos, banco de registros y ALU.

En este video se muestra como se calcula el tiempo de ciclo para la instrucción LW del procesador R-MIPS.

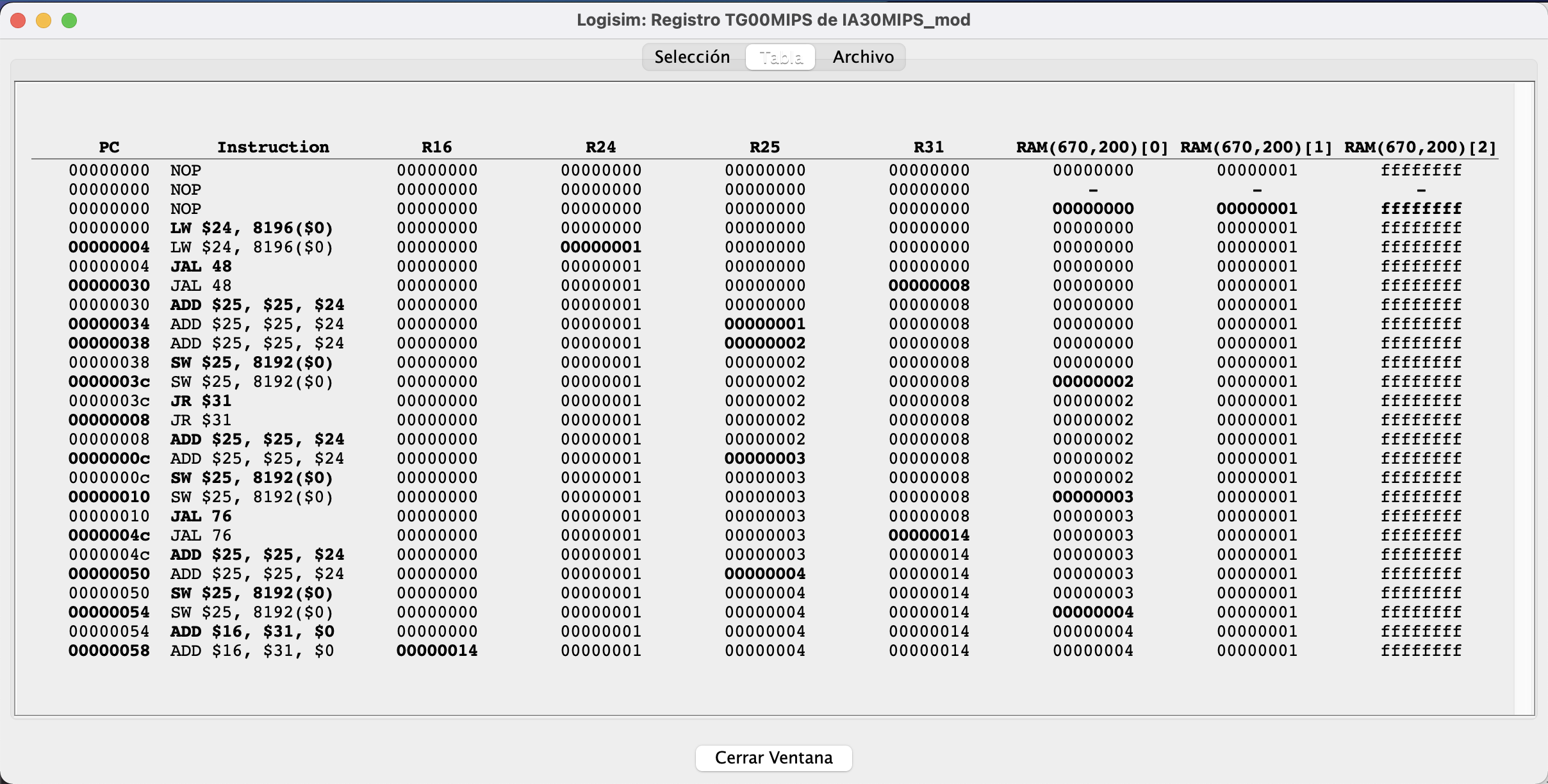

Aquí os presento un ejemplo de simulación de la ejecución de un programa en el procesador R-MIPS en logisim y la depuración de errores en el diseño.

A continuación presentamos un par de utilidades para facilitar la programación y simulación del procesador R-MIPS

Esta web permite:

Modificación del programa Logisim para poder ver en la simulación con tabla el nemotécnico ensamblador de las instrucciones simuladas (Cambiar base del bus correspondiente a 32).